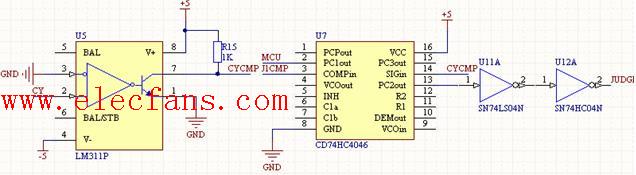

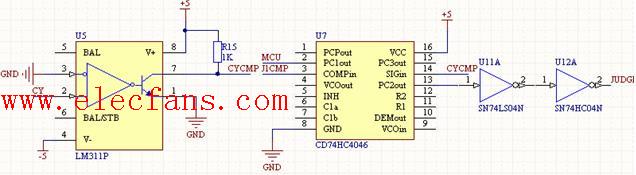

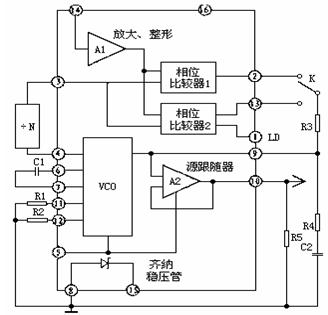

過零比較和相位比較電路原理圖

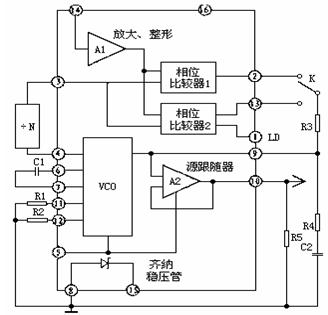

現在常使用集成電路的鎖相環CD4046,是通用的CMOS鎖相環集成電路,其特點是電源電壓范圍寬(為3V-18V),輸入阻抗高(約

1腳相位輸出端,環路入鎖時為高電平,環路失鎖時為低電平。2腳相位比較器Ⅰ的輸出端。3腳比較信號輸入端。13腳相位比較器Ⅱ的輸出端。14腳信號輸入端。對相位比較器Ⅱ而言,當14腳的輸入信號比3腳的比較信號頻率低時,輸出為邏輯“

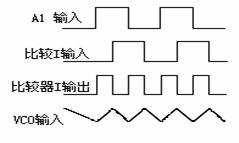

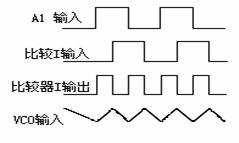

圖2.13 比較器輸出波形圖

現在常使用集成電路的鎖相環CD4046,是通用的CMOS鎖相環集成電路,其特點是電源電壓范圍寬(為3V-18V),輸入阻抗高(約

1腳相位輸出端,環路入鎖時為高電平,環路失鎖時為低電平。2腳相位比較器Ⅰ的輸出端。3腳比較信號輸入端。13腳相位比較器Ⅱ的輸出端。14腳信號輸入端。對相位比較器Ⅱ而言,當14腳的輸入信號比3腳的比較信號頻率低時,輸出為邏輯“

圖2.13 比較器輸出波形圖

評論