基于FPGA的QCM濕度測量系統程序設計與仿真

摘要:為了實時檢測常溫下的濕度,以便負責人根據需要調整環境狀態。采用測頻計數法結合頻差法設計了以FPGA芯片(EP2C8Q208C8N)為基礎的可用于濕度測量的石英晶體諧振頻率漂移檢測電路。重點介紹在FPGA平臺上通過測量石英晶體的諧振頻率來間接測量濕度的方法,討論了FPGA平臺上的每個模塊的設計過程,給出了部分模塊和整體電路的仿真圖,解釋了仿真結果。FPGA參與外圍硬件電路的輔助設計,會使設計更加簡單,周期更短。

本文引用地址:http://www.j9360.com/article/201610/309096.htm濕度若能夠實時進行測量,對于生產、生活方面是很至關重要的,尤其是在那些倉儲、種植、養殖、家庭、醫療、科研等關注濕度變化的地方。如果異常濕度不能及時被測量到,就會使生產降低、身體感到不適。現代濕度測量從機械式發展為精確度更高的電子式濕度傳感器。石英壓電諧振式濕度傳感器就是利用了諧振元件的固有頻率與被測量之間存在關系而進行測量的一種電子裝置。通過在線可編程芯片FPGA來對傳感器數據進行采集、測量和處理,能極大地整合和簡化系統設計。文中將主要描述石英晶體(QCM)濕度測量系統中FPGA部分的程序設計,分別給出單個模塊的設計思路和(或)工作流程圖,對部分模塊給出仿真結果,最后對總體程序進行了仿真,給出整體結果。

1 基本原理

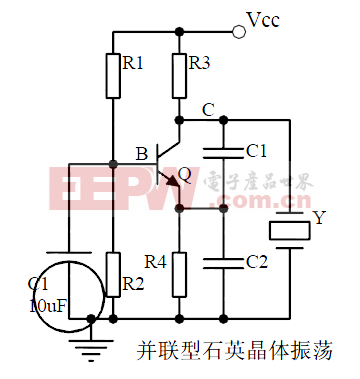

在壓電石英晶體的晶片表面涂覆濕度敏感材料,制成一個附著有吸濕膜的石英晶體諧振器。若該石英晶體放置于濕度環境中,由于吸濕膜通過氫鍵或者分子間作用力吸附了環境中的水汽分子,使得石英晶體的質量發生變化。根據Sauerbrey公式,如式(1)所示,為晶片上吸附水汽分子后石英晶體質量變化量,Fo為基頻,△f為相同基頻下的無濕敏膜標準石英晶體諧振(以下簡稱標準晶振)頻率Fo與有濕敏膜傳感石英晶體諧振(以下簡稱傳感晶振)頻率的頻率差,S為晶片上濕敏膜的面積。石英晶體的質量若發生變化,其諧振頻率也會隨之發生變化。只要通過測量出石英諧振頻率的變化量,再利用頻率差-質量差-相對濕度三者之間存在的關系,由頻率轉換得到相對濕度。

系統由濕度傳感器、QCM振蕩電路、FPGA平臺、顯示電路等模塊組成,如圖1所示。FPGA平臺將集成測量、控制、驅動等功能模塊,先通過參比對照測出兩個通道的頻率值,再計算兩通道頻率值的差,根據轉換表轉換出相對濕度值,送出顯示。采用基頻10 MHz,AT切型的石英晶體作為濕度傳感器。

2 總體方案構造

2.1 FPGA芯片

FPGA,通過軟件輔助編程的方式實現電路功能的一種半定制ASIC芯片。FPGA是在線可編程器件中的一種,基于查找表LUT的電路原理。N輸入的查找表,將輸入的真值表存儲在SRAM中,系統通過“查表”的方式,輸出預存結果。FPGA在電路設計和使用的過程中高度體現了以專用性、高效性,以人為本的設計思想。FPGA芯片采用的是美國Altera公司設計生產的Cyclone II系列中的EP2C8Q208C8N。它含有516個可編程邏輯塊CLBs,8256個邏輯單元LEs,165888個存儲位,138個可使用的I/O端口,端口最大電壓為3.3 V,核心電壓為1.2 V,工作適宜溫度為0~85℃。

2.2 FPGA總體電路構建

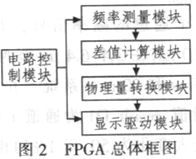

FPGA程序設計是整個相對濕度測量系統設計中關鍵的一部分,集成了控制、測量與鎖存、差值計算、物理量轉換,顯示驅動等模塊。通過軟件編程輔助設計的電路,既可降低硬件電路設計的成本,同時也發揮軟件設計帶來的優點。另外用FPGA做設計還可隨時就應用過程中出現的問題調整程序,使系統作更大優化。整個FPGA運行的流程圖如圖2所示。整個FPGA電路模塊的設計和仿真都將在Quartus II 9.0軟件環境下完成。在FPGA中相對濕度的測量將采用實時測量的方案。

3 模塊設計與仿真

3.1 控制模塊

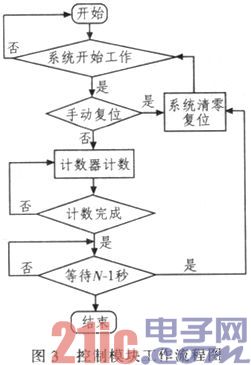

控制模塊主要完成對FPGA工作進程的控制。它包括系統啟動/暫停、使能控制、系統復位等功能,其工作流程如圖3所示。其中N值大小可以因需求不同作數值調整。

3.2 測量與鎖存模塊

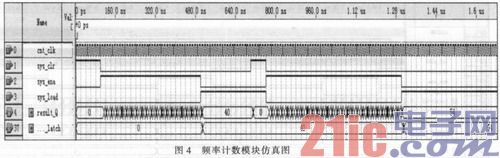

測量模塊是FPGA設計中最關鍵的模塊之一。為得到頻率差,采用雙通道分別進行標準晶振和傳感晶振的頻率測量。數據信號在一個閘門內的計數值很大,所以不考慮因閘門信號與數據信號不同步造成的±1字的誤差。測量模塊中的頻率測量采用直接計數法完成。在使能高電平期間,頻率信號觸發沿每到來一次時,計數器加1計數;在使能低電平期間計數器數據鎖存,保存至下一次的測量完成。最小測量精度為1 Hz,采用8421BCD碼計數(便于觀察和后續電路設計)。

對測量和鎖存模塊進行仿真分析,如圖4所示。從圖中可以看出系統在異步復位信號sys_clr高電平下復位,否則在使能信號sys_ena高電平有效時,系統計數,直到使能無效,result_Q最后一個計數值送入鎖存器result_latch保存至下一次測量結束。在整個系統中復位信號周期性出現在保持時間末刻,以使計數寄存器下一次從0開始計數。

3.3 頻率差值計算模塊

獲得兩個通道的頻率值后,根據頻差計算公式(2),將兩者送入減法器中。

△F=Fo-Fs (2)

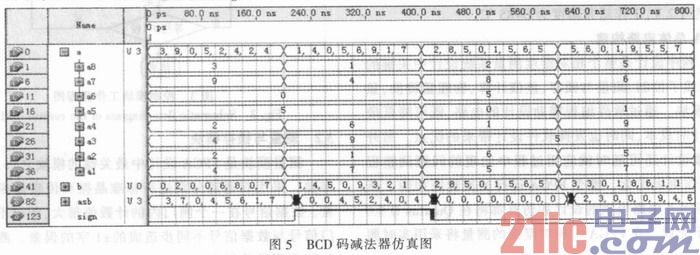

減法器采用BCD碼減法,按以下規則順序執行:

1)比較大小,如果被減數大于或等于減數,差為正,符號記為0;如果減數小于被減數,將被減數與減數的位置對調,差為負,符號記為1;

2)按照二進制法逐位減法運算;

3)從最低位開始包括被減數、減數、差的每4位組成一組,高位不夠4位用零補齊;

4)如果每一組的被減數大于減數,則若差大于9,則差減去6,其他不變;

5)如果每一組的被減數小于等于減數,則若差大于5(最小1組大于6),則差減去6,其他不變;

6)修正后的結果即為頻率差。

隨機設計了幾組數據進行仿真測試,如圖5所示,經比對,結果正確。其中a8至a1為被減數a的高位至低位,即為標準晶振的頻率值;b8至b1為減數b的高位至低位,即為傳感晶振的頻率值;差為asb8至asb1,符號為sign。

3.4 物理量轉換模塊

在20%至85%這段相對濕度區間,頻率差與相對濕度值之間的曲線接近線性。設計中頻率差與相對濕度值之間的轉換以查找表的形式來實現,一個濕度范圍對應一組頻率差。通常情況下,由于材料、制作工藝的不同,頻率差的變化也會有所不同。為了仿真,假定相對濕度變化1%時,頻率差變化2個值。

3.5 顯示驅動模塊

后端顯示用LCD1602液晶屏構成。由于1602中命令和數據共享總線,首先需要對其初始化,目的就在于對總線狀態、顯示樣式的設置。初始化過程為清屏→顯示狀態設置→工作方式設置→CG RAM設置→DD RAM設置。一旦初始化結束后,就可以將結果等內容在液晶屏上動態顯示。

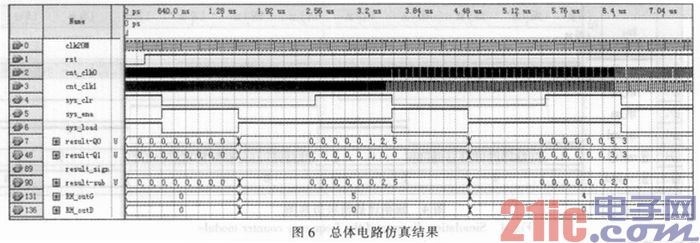

4 總體電路測試與仿真

為便于仿真觀察,程序上對時鐘和信號周期進行了修改,但設計思路不變,不影響整個的工作流程。打開Quartus II的仿真器,插入輸入輸出信號,依照實際情況給出輸入信號波形,仿真結果如圖6所示。其中clk20M為20 MHz的時鐘信號,經20分頻,得到一個周期為的閘門信號(實際中為2s)。因為傳感石英晶體質量因受濕度的影響而增加,其諧振頻率隨之下降,故傳感晶振頻率總小于標準晶振。cnt_clk0、cnt_ clk1分別為兩個通道的頻率信號,其周期設置在0 s~3.4μs為8 ns和10 ns,在3.4~6.4 μs至為19 ns和30 ns,在6.4~7.3μs至為35 ns和50 ns;系統一開始清零;result_Q為通道0的頻率測量值,result_Q1為通道1的頻率測量值。在仿真中取頻率的最大變化為50,每1%的相對濕度,有2的變化。由圖可看出,當系統在接到清零信號后,立即對計數寄存器進行了數據復位。當測量周期結束后,分別得到以下數值:在0 s~3.4μs這一段,通道0計數值為125,通道1為100,差值為25,濕度為50%;在3.4~6.4μs至,通道0為53,通道1為33,差值為20,濕度為40%。

5 結論

設計運用了功能強大的FPGA作為濕度測量系統的主要部件,充分發揮其高度集成的內部資源和彌補了硬件上設計的漏洞和誤差。文中對相對濕度測量系統中的FPGA部分的程序進行了設計說明和仿真,給出總體電路的仿真結果。證明了設計方案的可行性,體現了軟件結合設計所帶來的簡便性和實用性。

如果將該FPGA測量平臺與其他外圍硬件電路組合,即可完成濕度測量系統的設計,同時也可用于特殊氣體的檢測。

評論