基于ARM的便攜式1553B總線測試系統的設計與實現

摘要:為了方便對1553B設備進行測試,介紹了一種基于ARM9平臺和FPGA的1553B總線測試系統的設計與實現方法。該系統以LPC3250作為微處理器,以CYCLONE I系列的EP1C6Q240C8芯片實現ARM與1553B協議芯片的接口邏輯。在Linux操作系統2.6群訟率迪1553B的驅動程序。15 53B協議芯片采用BU-64843T8,以實現系統的便攜性。

本文引用地址:http://www.j9360.com/article/201610/308999.htm隨著航空電子系統的發展,多路數據傳輸數據總線在航空電子系統中起著越來越重要的作用,其主要特點是集中控制、實時性要求高、分布處理。1553B總線以其具有較高的可靠性和靈活性,廣泛應用于軍事、航空航天系統。傳統的1553B測試設備采用普通計算機或工控機作為測試平臺,通過PCI總線與被測設備通信,這對測試設備的攜帶造成極大不便。本文所闡述的測試系統以ARM9作為中央處理器,以DDC的BU-64843T7作為1553B協議芯片,從而實現系統的小型化和便攜化,應用FPGA實現ARM時序與1553B時序的轉換,并采用Linux操作系統以確保系統穩定可靠。

1 ARM與FPGA數據通信接口設計

1. 1 系統硬件介紹

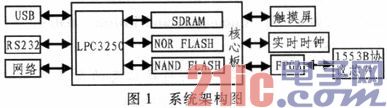

該系統硬件由LPC3250核心板、外擴接口電路、FPGA和1553B協議芯片組成組成。系統架構如圖1所示。

LPC3250微處理器面向低功耗、高性能的應用,采用ARM926EJ-S CPU內核,實現5級流水處理并采用哈佛結構,可工作在266 MHz的頻率下,數據處理能力強大。

本系統外擴USB、RS232和網絡接口,用于操作系統的燒寫和驅動程序、應用程序的調試,并且配備實時時鐘,可以掉電保持。為增加其可靠性,本系統在多處增加ESD芯片,以增強系統的抗靜電能力。

FPGA采用Altera公司的Cyclone I系列的EP1C6Q240C8芯片,該系列芯片具有20 060個邏輯單元以及288 kb RAM,支持3.3V LVTTL/CM OS IO標準,可直接與ARM通信,無需進行電平轉換。

1553B協議芯片選擇DDC公司的BU-64843T8芯片。該芯片是世界上第一個將1553B協議芯片和隔離變壓器集成到一體的芯片。因此,在布PCB時,會節省很大空間,從而使系統小巧,方便攜帶。

1.2 接口電路設計

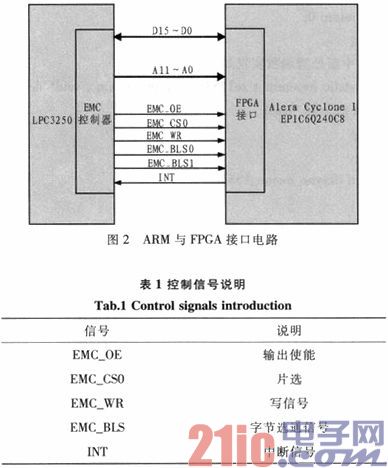

LPC3250包括3個外部存儲器接口,分別是NAND Flash控制器、Secure Digital控制器和外部存儲器控制器(External memory controll er,簡稱為EMC)。EMC提供了系統總線與片外存儲設備之間的接口功能,可實現與SDRAM、DDR SDRAM和SRAM設備的通信。該系統采用EMC的靜態RAM接口與FPGA進行通信,該接口具有時序操作簡單,接口速度快等特點。利用FPGA模擬靜態RAM,并進行時序轉換,從而實現ARM對1553B芯片的訪問。圖2為ARM與FPGA的接口電路圖,由于1553B芯片內部RAM為4K*16bit,因此數據線選用16位,地址線選用12位。通過EMC靜態存儲器控制器的配置寄存器,可將數據總線分別設置為8位、16位、32位。該系統需將配置寄存器的低兩位設置為01,即16位總線。其他控制信號說明見表1所示。

1. 3 FPGA邏輯設計

若想成功訪問1553B設備,必須嚴格按照1553B時序進行操作,然而EMC的時序與1553B的時序差異很大,因此需要進行時序轉換,這通過一片FPGA來實現。BU-64843T8的控制信號主要包括,TRANSPARENT/BUFFERED*、STRBD*、SELECT*、RD/WR*、MEM/REG*、IOEN*、READYD*、ADDR_LAT/MEMOE*.RT_AD_LAT*,INT*等信號。

TRANSPARENT/BUFFERED*信號用于設定芯片工作在透明模式還是緩沖模式,該系統的1553B不需外擴存儲器,工作在緩沖模式下即可,因此MEMOE*等信號可以不做考慮;STRBD*和SELECT*可接到一起,作為芯片的片選信號;RD/WR*為讀寫信號;MEM/REG*用來區分訪問內部4K存儲器資源還是寄存器資源;IOEN*有效時,標志芯片正在處理外部的訪問;READYD*信號在本系統中十分重要,當ARM寫時,READYD*有效表示數據成功寫入芯片中,當ARM讀時,READYD*有效表示數據線上的數據有效,可以使用;ADDR_LAT為地址鎖存信號,對于總線未復用的處理器,該信號置為高;RT_AD_LAT*信號為RT地址鎖存信號,該信號出現上升沿,即可將RT地址上的數據鎖存到芯片內部,因此RT地址無需一直保持著。INT*信號用于中斷ARM,該信號經過FPGA與ARM的GPIO引腳相連,相應的GPIO引腳被配置為外部中斷引腳。

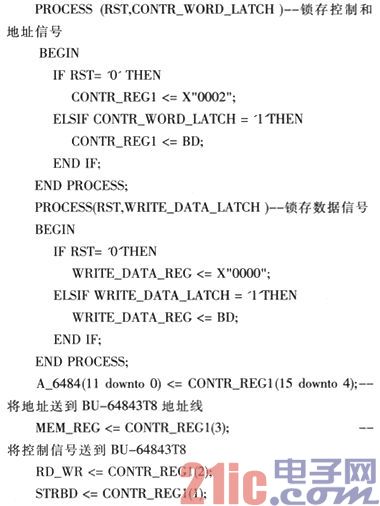

FPCA的邏輯設計采用鎖存的方式,即所有的地址信號、數據信號、讀寫、片選、EME/REG*信號通過鎖存器直接打到總線上,這些信號在ARM訪問期間一直有效。因此ARM需要進行多次寫操作:先把要寫的數據送出,再把要訪問的地址和控制信息送出,之后循環讀取READYD*信號,直到其有效,再進行下一次讀寫操作。相關的VHDL代碼如下:

2 1553B驅動程序的開發原理與實現

2.1 文件操作接口

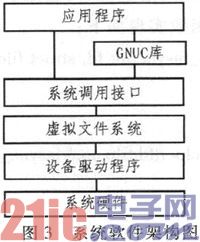

設備驅動程序在Linux內核中扮演著特殊的角色。它們是獨立的模塊,使某個特定的硬件響應一個定義良好的內部編程接口,用戶的操作通過一組標準化的調用執行,而這些調用獨立于特定的驅動程序。將這些調用映射到作用于實際硬件的設備特有操作上,則是設備驅動程序的任務。系統軟件架構如圖3所示。

Linux驅動程序支持3種類型的設備:字符設備、塊設備和網絡設備。字符設備是個能夠像字節流一樣被訪問的設備。字符設備驅動程序通常要實現open、close、read、write系統調用。本系統的1553B設備屬于字符設備,它的驅動程序主要包括以下幾個模塊:初始化模塊、打開關閉模塊、讀寫模塊、中斷處理模塊。

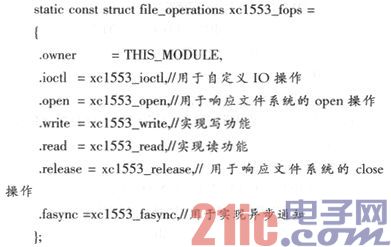

驅動程序與應用程序的通信主要通過系統函數調用,Linux為所有設備文件提供統一的操作函數接口,我們的驅動程序中只需實現struct file_operations中相應的函數即可,主要包括ioctl、read、write、open、release、fasync函數。具體C語言代碼如下所示:

當用戶加載驅動模塊時,一系列初始化工作在static int_init xc1553_init(void)函數中完成,包括設備注冊,物理地址到虛擬地址的映射,EMC模式的配置,中斷處理函數的注冊。

當用戶卸載驅動模塊時,需要在static void_exitxc1553_exit(void)函數中進行驅動模塊和設備的卸載,以及中斷號的釋放。

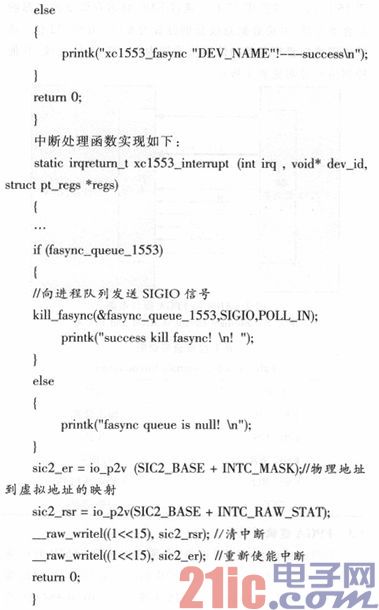

2.2 中斷處理模塊的實現

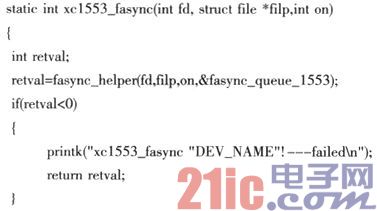

當1553B產生中斷時,由xc1553_init函數中注冊的中斷處理函數進行處理,并且通知上層應用程序進行讀寫操作。驅動程序與應用程序的通信通過異步通知的方式實現。為了實現異步通知,在驅動程序中需要實現int fasync_helper(int fd,struct file*filp,int mode,stru ct fasync_struct**fa)和voidkill_fasync(struct fasync_struct**fa,int sig,int band)函數。

fasync_helper函數在xc1553_fasync中實現,作用是為當前進程創建一個fasync_struct結構體,然后掛入目標設備的fasync隊列,最后在設備驅動的中斷處理程序中,使用kill_fasync函數向該隊列發送信號,通知上層應用程序。

xc1553_fasync函數實現如下:

3 結束語

1553B總線廣泛應用于航空領域,基于1553B總線的測控設備普遍體積大,攜帶不方便,本文所闡述的測試系統完全能夠實現傳統測控設備的功能,并且極大的縮小了設備的體積,方便攜帶。經過測試,該系統實時性高、工作穩定,能夠滿足軍工要求。

評論