基于FPGA的速度和位置測量板卡的設計與實現

摘要:針對增量式光電編碼器經典速度測量算法M/T法低速采樣時間過長和位置測量算法精度不高的問題,本文基于定采樣周期M/T法設計實現了速度和位置測量板卡。采用Xilinx公司的XC3S400 FPGA為核心控制芯片進行設計,并設計PC104總線接口實現板卡與控制器的數據通信。該板卡接收處理光電編碼器的反饋脈沖得到速度和位置參數,將數據通過PC104總線接口傳遞給控制器。實驗表明,板卡的最小采樣時間達到1ms,并且位置測量精度可達5×10-3。

本文引用地址:http://www.j9360.com/article/201610/308996.htm增量式光電編碼器作為速度和位置傳感器被廣泛應用于伺服系統。理論上,光電編碼器反饋脈沖的頻率對應被測軸轉速,反饋脈沖個數的累加值對應位置信息。經典的速度測量方法有M法、T法和M/T法3種:其中M法通過計取固定時間間隔內光電編碼器的反饋脈沖數計算當前轉速,適用于高速場合;T法利用高頻脈沖測量相鄰反饋脈沖的時間間隔計算當前轉速,適用于低速場合;M/T法不僅測量固定時間間隔內反饋脈沖的增量值,而且計數該時間內的高頻脈沖數。雖然M/T法克服了M法和T法測速范圍有限的缺點,在高速和低速段都具有較高的分辨率及較低的測速誤差,但是存在低速采樣時間過長等問題。經典的位置測量方法按轉向的正負對反饋脈沖進行增減計數,然后將計數值乘以脈沖當量K得到當前位置信息,可見其測量精度取決于脈沖當量。

本文以定采樣周期M/T法為基礎,它解決了經典M/T法低速檢測時間過長的問題,保證每一固定周期都能采樣到數據。此外,該算法充分利用反饋脈沖的位置信息和時間信息,得到了比一個脈沖當量K更為精確的位置信息。本文利用FPGA設計實現定采樣周期M/T法,并設計PC104總線接口滿足板卡與控制器數據通信的要求。

1 總體方案

速度和位置測量板卡接收光電編碼器的反饋脈沖信號,通過差分電路將其轉換為單端信號消除共模干擾,然后在FPGA中對脈沖處理得到速度和位置參數,最后將參數通過PC104數據接口傳遞給控制器。速度和位置測量板卡除差分電路以外的功能均通過FPGA設計實現(如圖1所示),因此FPGA是本板卡的核心芯片。速度和位置測量板卡主要包括倍頻辨向模塊、定采樣周期M/T法模塊和PC104數據接口模塊。

1. 1 倍頻辨向模塊

光電編碼器的輸出反饋脈沖包括相位差90°的A、B信號以及零位脈沖Z。A、B之間的相位關系標志被測軸的轉向,即A相超前B相90°表示正轉,滯后90°表示反轉;Z脈沖起到參考零點的作用。一個周期內A、B兩路信號的相對位置變換了4次,即正轉A、B按00-10-11-01循環輸出,反轉遵循00-01-11-10的規律。倍頻辨向模塊通過檢測A、B信號的狀態變化輸出四倍頻及方向信號,不僅提高了速度和位置測量的精度,還起到抗干擾的作用。

1.2 定采樣周期M/T法模塊

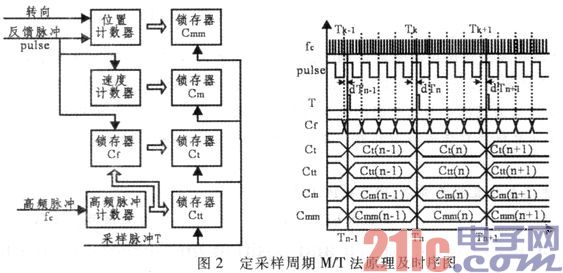

定采樣周期M/T法模塊分為速度測量電路和位置測量電路兩部分,圖2給出了該算法的硬件原理及時序圖。定采樣周期M/T法對高頻脈沖fc兩級鎖存的設計確保實際檢測起始點Tk超前于采樣周期Tn,這解決了M/T法在低速時檢測時間過長的問題,保證每個采樣周期內都能成功采集到數據。

速度測量硬件電路由速度計數器及其數據鎖存器Cm,以及高頻脈沖計數器及其兩級數據鎖存器Cf和Ct構成;其中速度鎖存器Cm和高頻脈沖鎖存器Ct由采樣脈沖觸發,輔助高頻脈沖鎖存器Cf由反饋脈沖觸發。通過差分處理得到當前周期Tn內的轉速增量Cm和高頻脈沖增量Ct,并設高頻脈沖的頻率為fc,脈沖當量為K,那么計算可得轉速為:

Vn=KxfcxCm/Ct

位置測量硬件電路同樣采用高頻脈沖的兩級鎖存設計,除此之外還包括位置計數器及其數據鎖存器Cmm,以及輔助位置鎖存器Ctt。由圖2可知,dTn-1和dTn這兩個時間差所對應的位置變化小于一個脈沖當量K,位置測量算法將上述時間差內的位置變化加入到位置信息中,提高了位置測量的分辨率和精度。dTn通過差分當前周期輔助位置鎖存器Ctt和脈沖鎖存器Ct得到,接著將dTn乘以速度值Vn可得位置變化。位置鎖存器Cmm計取了反饋脈沖的變化值,再加上dTn-1和dTn內位置變化,便能計算出精確的位置信息。

dTn=(Ctt(n)-Ct(n))/fc

S=KxCmm+VnxdTn-Vn-1xdTn-1

2 各個模塊Verllog實現

根據速度和位置測量板卡的總體設計方案,利用Verilog設計實現各模塊。

2.1 倍頻辨向模塊

本模塊在FPGA系統時鐘clk上升沿檢測A、B的電平,并與上一clk記錄的狀態進比較:當狀態變化符合00-10、10-11、11-01、01-00時,表明A超前B相90°,并且A或B產生一個邊沿跳變,此時光電編碼器正轉那么置1方向信號,同時輸出一個計數脈沖,這樣一個周期內將產生4個計數脈沖實現了四倍頻;當變化對應00-01、01-11、11-10、10-00時,標志A滯后B相90°,光電編碼器反轉則清零方向信號,并輸出一個計數脈沖;當變化符合00-00、01-01、10-10、11-11時,說明光電編碼器處于換向階段,或者對應正反轉的中間狀態,此時保持方向信號并且不輸出計數脈沖;當變化為00-11、01-10、10-01、11-00時,說明A、B信號受到干擾而產生了錯誤的狀態翻轉,此時保持方向信號并且不輸出計數脈沖,達到了抗干擾的目的。

2.2 定采樣周期M/T法模塊

分析定采樣周期M/T法模塊可知,它主要由計數器和鎖存器組成,其中計數器對脈沖個數進行計數,得到的計數值存于鎖存器中等待數據接口模塊讀取。

按計數方式的不同,計數器又可細分為增計數器和可逆計數器。其中高頻脈沖計數器和速度計數器都采用增計數,在檢測到計數脈沖有效時加1計數值。位置計數器采用可逆計數的方式,在計數脈沖有效時通過方向脈沖決定采取增或減計數。由于對增量式光電編碼器的反饋脈沖計數只能獲得轉臺的相對位置,因此在計數器斷電或控制系統上電之前,都要對計數器所存數值進行校正,即歸零。為了實現歸零操作,計數器除可逆計數外還需具備清零以及置數等功能。

鎖存器在采樣脈沖T有效時,鎖存當前數據供接口電路讀取,其中采樣周期大小取決于控制器對速度和位置的讀取頻率。考慮到數據讀取的安全性,控制器讀操作前必須首先完成各鎖存器的數據鎖存工作,即通過控制器對板卡的寫信號產生采樣脈沖T觸發鎖存器的鎖存工作。

本模塊設計了4個雙字鎖存器暫存速度和位置參數,因此開辟4個雙字的I/O地址空間。控制器對I/O地址的讀操作實現鎖存器數據的讀取,寫操作為板卡提供清零、置數及采樣脈沖等信號。

2.3 PC104數據接口模塊

PC104總線是一種專為嵌入式控制而定義的工業控制總線,它具有小尺寸結構、抗震性極佳的堆棧式連接、低功耗總線驅動等優點,廣泛應用于機載設備的開發中。此外,它是一個8位和16位兼容的總線,本模塊采用8位總線方式,采用以下總線信號完成通信設計:SD7~SD0:數據信號;SA9~SA0:地址信號;AEN:地址使能信號;IOR:I/O讀信號;IOW:I/O寫信號;電源信號。

在PC104系統中,為防止I/O地址沖突,每個模塊都必須有一個單獨的基地址。速度和位置測量板卡采用10位地址譯碼,基地址通過板卡上的基地址跳線器進行設置。PC104數據接口采用I/O讀寫方式進行通信,利用狀態機設計實現本模塊如圖3所示。S0為空閑狀態,此狀態為初始狀態,一旦控制器對板卡進行操作,則進入S1狀態。S1狀態記錄控制器的地址、數據以及控制信號,并判斷控制器的操作類型。如果是讀操作進入S2狀態,若是寫操作則進入S3狀態。在S2狀態中,將對應地址的數據給到數據線,完成讀操作。在S3狀態,將數據寫入對應地址中,完成寫操作。讀操作或者寫操作完成之后,狀態又重新回到S0,等待控制器下次讀寫。

下面結合PC104的信號說明各狀態的作用。S0狀態檢測地址使能信號AEN,當AEN有效并且地址信號SA的高位與基地址一致,說明控制器對本板卡操作,則激活S1狀態。S1狀態記錄地址信號SA的低4位和數據信號SD,并判斷讀信號IOR或寫信號IOW是否有效。當IOR有效說明目前進行讀操作進入S2狀態,而IOW有效表明當前為寫操作進入S3狀態。S2狀態對地址進行分支選擇確定欲讀取數據的地址,輸出對應地址的數據完成讀操作。S3狀態將數據寫入到對應地址完成寫操作。

3 測試平臺與仿真測試

用ISE軟件編程實現各模塊的功能,用ModelSim對其進行仿真測試,圖4為仿真結果。由圖可知,輸入的A、B信號模擬正轉、反轉及干擾三種狀態,正轉和反轉下每周期都將輸出四個脈沖,并且正轉方向信號置1,反轉清零,而在干擾信號下不輸出計數脈沖,并且方向信號保持不變。速度計數器在計數脈沖有效時計數,位置計數器根據方向信號對計數脈沖做增減計數,速度鎖存器Cm、位置鎖存器Cmm在采樣周期有效時鎖存速度和位置值。輔助高頻脈沖鎖存器Cf及高頻脈沖鎖存器Ct對高頻脈沖進行兩級鎖存,保證實際采樣點超前于采樣周期,保證每個周期下都能采樣到數據。

設計完成的速度和位置測量板卡如圖5所示,FPGA采用Xilinx公司的XC3S400,控制器部分選用盛博公司的SAT-1040板卡。使用36000刻線的增量式光電編碼器,高頻脈沖由40 MHz晶振提供,最小采樣周期可達1ms,在測量范圍內速度、位置測量精度分別達到3x10-5、5x10-5。

4 結束語

文中以FPGA為核心控制芯片設計實現了速度和位置測量板卡,它以定采樣周期M/T法為基礎對光電編碼器的反饋脈沖處理得到表征速度和位置的參數,通過PC104總線接口將數據傳遞給控制器計算得到精確的速度和位置信息。整個設計在FPGA內完成,故硬件結構簡介,可靠性強,抗干擾能力強;板卡的最小采樣時間達到1 ms,確保每一周期下都能采樣到可靠數據,并將位置測量精度提高至5x10-5。

評論