用于多站點并行測試的 ACS集成測試系統(一)

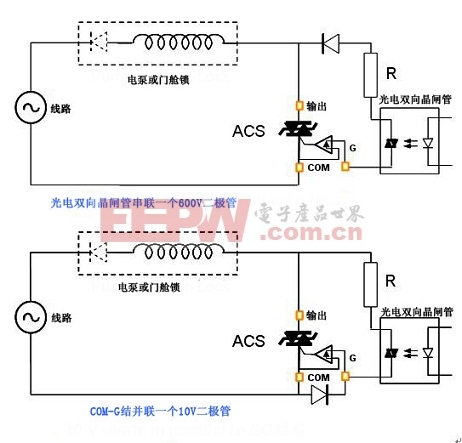

圖1. 此例中的ACS集成測試系統配置為并行、多站點 測試,非常適于這些應用: • 多站點參數管芯分選 • 多站點晶圓級可靠性測試 • 多站點小規模模擬功能測試

行業面臨的挑戰

測試成本被視為未來先進半導體的 首要挑戰。對測試成本和測試系統購置成本影響最大的是測試系統吞吐量。不 論什么具體應用,并行測試都最大程度 改善了晶圓上測試的吞吐量公式。這是 因為大部分開銷用在了移動探針或者將 探針重新定位至下一個測試站點。開銷包括了探測器和耗材(例如探針卡)的 成本和維護。最重要的是如何最大程度 利用這些投入。提高測試儀的吞吐量能 顯著降低測試成本,縮短產品面市時間。

解決方案的理念

首先,考慮被測器件(DUT)。DUT常 常包含大量待測元素。在順序測試架構中, 無論測試多么簡單的元素都會增加總測試 時間。如果兩個相同元素可以并行測試,甚至更好的情況是,如果物理位置相鄰的 兩顆相同芯片(如圖2所示)可以并行測試,那么測試總吞吐量將翻番。不僅測試 儀吞吐量翻番,而且探針移動次數也減半, 進而顯著提高了測試系統吞吐量。 非常重要的是重視芯片間可能出現的 寄生效應。例如,通過晶圓基底的耦合可能需要順序執行一些低電流測試。非常幸 運的是,多數測試不涉及低電流。 管理測試成本的另一個關鍵是考慮使 用現有或常規探測方案。例如,常規探針 卡能用于探測圖2中兩個芯片的20個引腳。 此原理可以擴展至更大數量的芯片,同時繼續使用現有的探測技術。

圖2. 并列的兩個小芯片站在常規探針卡容易到達的范 圍。在此情況下,可以并行測試每顆芯片中的兩個FET, 因而總吞吐量提高了400%。

評論