基于DDS芯片AD9852的雷達回波模擬器設計

摘要 基于直接數字頻率合成技術DDS的原理,分析了影響DDS頻率輸出的核心因素。在此基礎上仿真驗證了相位累加器的位數對DDS頻率輸出的作用。介紹了一種DDS芯片AD9852并基于這種芯片提出了一種雷達回波模擬器的設計,并分析了DDS芯片的優缺點。該設計能夠穩定地產生70 MHz載頻的雷達回波,較好地模擬出所需回波。

本文引用地址:http://www.j9360.com/article/201610/308168.htm直接數字頻率合成技術(DDS)是繼直接頻率合成技術和鎖相環式頻率合成技術之后的第三代頻率合成技術,它的原理是在采樣頻率一定的條件下,通過控制兩次連續采樣之間的相位增量來改變所得的離散序列頻率,然后經保持和濾波,唯一回復出該頻率的模擬信號。與其他頻率合成方法相比,直接數字頻率合成器具有頻率街邊速度快、頻率分辨率高、輸出相位連續、可編程和全數字化、便于集成等優點。本文在分析了DDS的基本原理的基礎上,提出了一種基于DDS芯片AD9852的雷達回波模擬器的設計。

1 DDS原理

1.1 DDS的基本原理

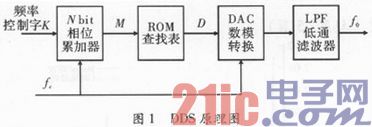

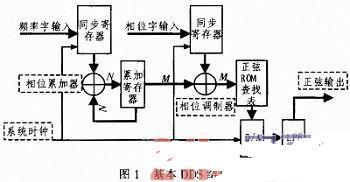

DDS的工作原理是基于相位與幅度的對應關系,通過改變頻率控制字K來改變相位累加器(位數為N)的相位累加速度,然后在固定時鐘的控制下取樣,取樣得到的相位值(取相位累加器的高M位)通過相位幅度(ROM查詢表法,即在ROM中存放不同相位對應的幅度序列,然后相位累加器的輸出對其尋址)。轉換得到相位值對應的幅度序列,幅度序列通過數模轉換及低通濾波得到余弦波輸出。DDS原理如圖1所示。

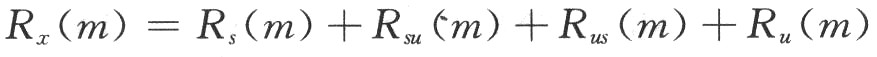

DDS的核心是相位累加器,它由一個N位相位加法器和一個N位相位寄存器組成。每生成一個時鐘脈沖(頻率為fc),加法器將頻率控制字K與寄存器輸出的數組相加,把相加的結果送到寄存器的數據輸出端。寄存器將加法器在上一個時鐘脈沖作用后產生的相位數據反饋到加法器的輸入端,以使加法器在下一個時鐘脈沖的作用下繼續與頻率控制字相加。這樣,相位累加器在時鐘脈沖的作用下,不斷對頻率控制字進行線性相位累加,當相位累加器產生一次溢出時,則完成了一次周期性操作,這就是DDS合成信號的周期,溢出頻率是DDS的輸出頻率f0。輸出頻率f0與時鐘頻率fc、頻率控制字K以及相位累加器位數的公式為

通過改變頻率控制字K,就可改變輸出頻率的值。由奈奎斯特采樣定理可知,DDS的最大輸出頻率為

fmax=fc/2 (2)

輸出信號頻率的分辨率即最低的合成頻率為

1.2 DDS的功能仿真

通過DDS的原理可知,實際運用中,輸出頻率f0、時鐘頻率fc以及相位累加器位數N均已知,則頻率控制字K為

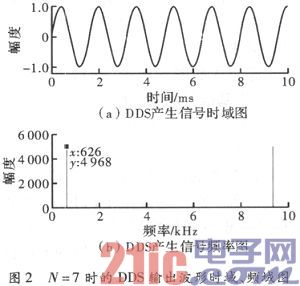

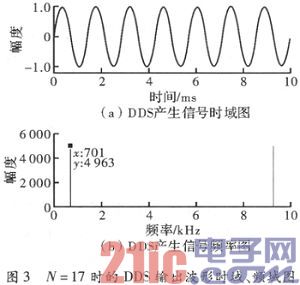

通過Matlab對DDS進行功能仿真,在相同的輸出頻率f0和時鐘頻率fc下,改變相位累加器的位數N,則頻率控制字K也改變,比較最后經過DDS仿真的輸出頻率f0。分別設置輸出頻率為700 Hz,時鐘頻率為10 kHz,相位累加器的位數分別設置為N=7和N=17,最后實際的輸出頻率如圖2和圖3所示。

由圖2和圖3比較可知,因相位累加器位數的不同,頻率控制字K也不同,DDS輸出的頻率就不同。相位累加器的位數N=7時,實際輸出的頻率只有626 Hz,距離預期輸出頻率700 Hz相差較大;而當N=17時,實際輸出的頻率為701 Hz,接近理想的輸出頻率700 Hz。因此可知,在相同的采樣頻率和預期的輸出頻率下,相位累加器的位數N決定了實際的輸出頻率。即相位累加器位數N越大,實際輸出頻率越接近預期輸出頻率。

2 AD9852芯片

AD9852數字合成器是一種高集成設備,它采用先進的DDS技術,配上高速、高性能的D/A轉換器來實現數字化可編程的合成器功能。當接入精確時鐘源時,AD9852能產生一種高穩定度的,頻率-相位-幅度-可編程的余弦波,這種波可用于通信、雷達中作為靈活的本振信號以及其他多種用途。AD9852的改進型-高速DDS芯片可提供48位頻率分辨率。截斷到17位的相位確保能產生優質的SFDR.AD9852電路結構,允許輸出信號的頻率達150 MHz,這使其數字上能以每秒100 MHz的速率調諧成新的頻率。

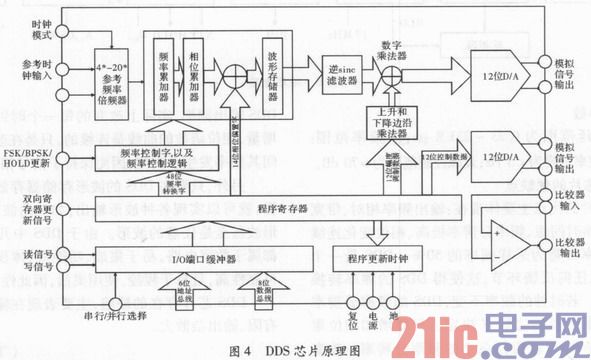

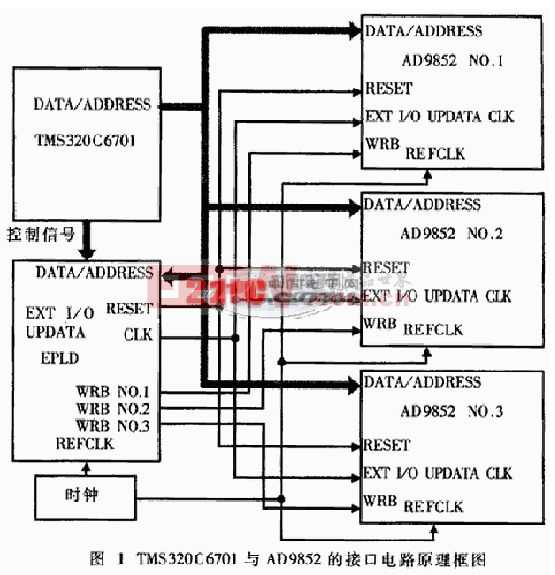

如圖4所示,AD9852內部包括一個具有48位相位累加器、一個可編程時鐘倍頻器、一個反sinc濾波器、兩個12位300 MHz DAC,一個高速模擬比較器以及接口邏輯電路。其主要性能特點如下:(1)300 MHz的系統時鐘。(2)能輸出一般調制信號,FSK,BPSK,PSK,CHIRP和AM等。(3)100 MHz時具有80 dB的信噪比。(4)內部有4~20倍的可編程時鐘倍頻器。(5)兩個48位頻率控制字寄存器,能夠實現較高的頻率分辨率。(6)兩個14位相位偏置寄存器,提供初始相位設置。(7)帶有100 MHz的8位并行數據傳輸口或10 MHz的串行數據傳輸口。

AD9852有40個程序寄存器,對AD9852的控制就是對這些程序寄存器寫數據實現的。通過并行總線將數據寫入程序寄存器時,實際只是暫存在I/O緩沖區中,只有提供更新信號,這些數據才會更新到程序寄存器。AD9852提供內部更新和外部更新兩種更新方式。內部更新通過更新時鐘計數器完成,當計數器計自減為零后會產生一個內部更新信號;外部更新需要在外部更新管腳上給予一個高電平脈沖。默認的更新模式為內部更新,可以通過設置控制寄存器0x1F的0位進行修改。

3 系統設計

3.1 系統組成

3.2 工作原理

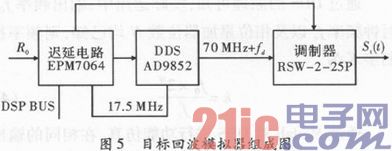

如圖5所示,17.5 MHz基準信號經直接數字頻率合成器(DDS,采用AD9852)輸出70 MHz+fd的目標回波模擬信號,輸出經脈沖調制器(采用MINI公司RSW-2-25P)形成目標回波信號St(t)。控制DSP通過總線(BUS)設置回波信號的遲延和DDS輸出信號的多普勒頻率。

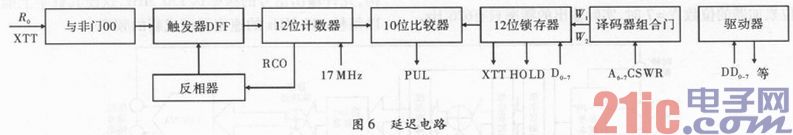

遲延電路組成如圖6所示。XTT=1時電路正常工作,距離同步基準信號R0的前沿使觸發器DFF翻轉,輸出高電平信號令12位計數器退出清零狀態開始對17 MHz時鐘計數。計數值的高10位(T0-9)與10位遲延時間鎖存器的值DE0-9進行比較,二者相等時輸出寬度為0.228 6μs的負脈沖PUL。計數器的進位信號RCO經反相后使觸發器復位。譯碼器對輸入的A6、A7、CS、WR信號譯碼,產生鎖存器的數據鎖存信號W0、W1。XTT信號為0時,電路關閉,無PUL信號輸出。HOLD供AD9852使用,同時對數據總線信號D0-7、WR、RD進行驅動后供AD9852使用。

3.3 系統參數

距離遲延范圍為0.23~233.8μs;fd頻率范圍:+400 kHz;頻率分辨為5 Hz;衰減控制范圍為>70 dB。

3.4 DDS芯片的優缺點

DDS芯片的優點主要體現在:輸出頻率相對、帶寬較寬頻率轉換時間短、頻率分辨率極高、相位變化連續等。輸出頻率帶寬為采樣頻率的50%。DDS是一個開環系統,無任何反饋環節,這使得DDS的頻率轉換時間極短。若時鐘的頻率不變,DDS的頻率分辨率就是由相位累加器的位數N決定。只要增加相位累加器的位數N即可獲得任意小的頻率分辨率。改變DDS輸出頻率,實際上改變的每一個時鐘周期的相位增量,相位函數的曲線是連續的,只是在改變頻率的瞬間其頻率發生了突變,因而保持了信號相位的連續性。

另外,只要在DDS的波形存儲器存放不同波形數據,就可以實現各種波形輸出,如三角波、鋸齒波和矩形波甚至是任意的波形。由于DDS中幾乎所有部件都屬于數字電路,易于集成、功耗低、體積小、重量輕、可靠性高,且易于程控,使用靈活,因此性價比較高。

DDS芯片存在的缺陷,主要表現在輸出頻帶范圍有限、輸出雜散大。

由于DDS內部數模轉換器(DAC)和波形存儲器(ROM)的工作速度限制,使得DDS輸出的最高頻有限。由于DDS采用全數字結構,不可避免地引入了雜散。其來源主要有3個:相位累加器相位舍位誤差造成的雜散;幅度量化誤差造成的雜散和DAC非理想特性造成的雜散。

4 結束語

在DDS原理的基礎上,提出了一種基于DDS芯片的雷達回波模擬器設計。該設計在實際運用中能夠穩定地產生所需要的回波。而且,由于DDS芯片所具有的優點,使得其簡單方便易于操作。隨著低價格、高時鐘頻率、高性能的新一代DDS芯片問世,它將在更新領域得到更廣泛的應用。

評論