一種模擬除法器的設計及仿真驗證CMOS工藝

本文設計了一種模擬除法器,在分析討論其工作原理的基礎上,采用CSMC0.5umCMOS工藝,對電路進行了Cadence Spectre 模擬仿真,仿真結果驗證了理論分析。

本文引用地址:http://www.j9360.com/article/201610/308108.htm1 電路的設計與分析

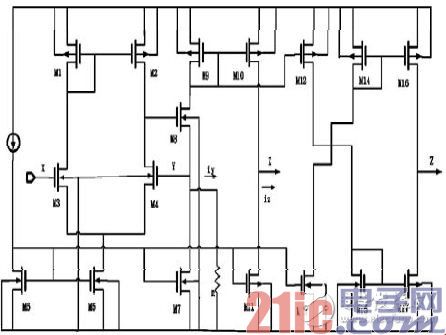

圖1 CCII 電路結構

模擬除法器由單電源+5V供電,主要由兩部分電路構成。第一部分為第二代電流傳輸器CCII,圖1 為CMOS CII電路。晶體管M3和M4 組成一個差分放大器,放大器的輸出經過晶體管M8 傳輸到Y端,而晶體管M1 和M2構成的電流鏡則是差分放大器的有源負載。假設晶體管M1 與M2、M3 與M4、M9與M10 是匹配的,晶體管M5、M6、M7 和M11 組成偏置電流鏡,分別為三個支路提供偏置電流,且I7=I11。晶體管M1、M2 組成的電流鏡迫使晶體管M3 和M4的漏源電流相等,于是有Vgs3=Vgs4,又晶體管M3 與M4 為源極耦合對,所以晶體管M3 與M4的柵壓相等,即Vx=Vy。晶體管M8作為源極跟隨器,在Y 端提供了低的輸出阻抗。如果Vy》0,且R是Y 端電阻,則從Y 端流出的電流為iy=Vy/R,晶體管M8 的漏極電流為(I7+iy),該電流通過電流鏡M9與M10 的作用復制到Z端。因為I11=I7,所以Z端流出電流與Y 端的電流相等,即iz=iy。

晶體管M12-M17組成交叉耦合電流鏡將電流(I7+iy)復制到Z端口,由于電流I16 跟隨電流I7 變化,因此電流iz 流動為反方向,即iz=-iy 。

由此,可以看出CCII 電路可以實現:

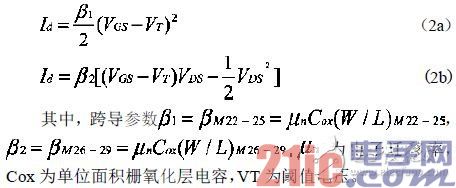

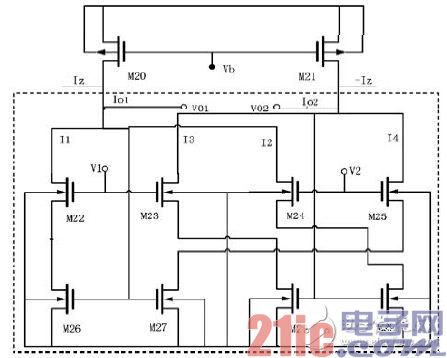

第二部分電壓電流轉換電路如圖2 所示,晶體管M20、M21 提供恒定且相等的電流源。晶體管M22-M25 工作在飽和區,M26-M29 工作在線性區。忽略體效應,則漏電流Id:

圖2 電壓電流轉換電路

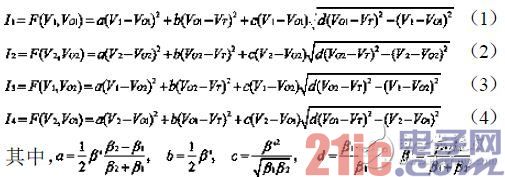

圖2 中虛線部分電路可分為四個支路,由晶體管對(M22,M26)(M23,M28)(M24,M29)(M25,M27)構成。電壓V1、V2為輸入信號。根據方程式(2a)和(2b),我們可以得到四個支路的電流與電壓的關系式:

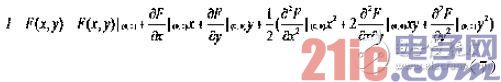

將等式(3)-(6)按照泰勒級數展開,如(7)式所示,將其在(0,0)點二階展開:

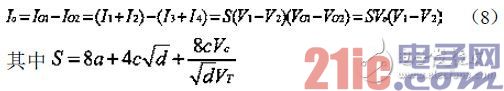

并對其路徑積分之后,總的差分輸出電流:

于是有,定義差分輸入V=V1-V2

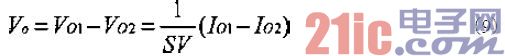

而差分輸入電流:

由方程式(9)、(10)、(11)和(1)有

評論