通過長距離I2C總線實現模擬信號的數字傳輸

內部集成電路總線(I2C)是一種同步串行數據通信總線,其中由主器件發起通信,從器件通過尋址機制加以控制。I2C總線上的節點很容易連接,因為只需連接兩條開漏形式的信號線(SDA用于數據,SCL用于時鐘)。這些線上的電容是限制傳輸速率和節點間距離的主要因素[1]。要想擴展速率和距離,有必要使用能夠識別數據方向的緩沖器。本文所述的設計案例充分展示了PCA9605緩沖器的優勢。

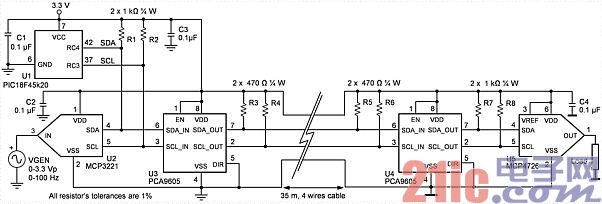

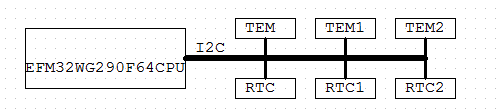

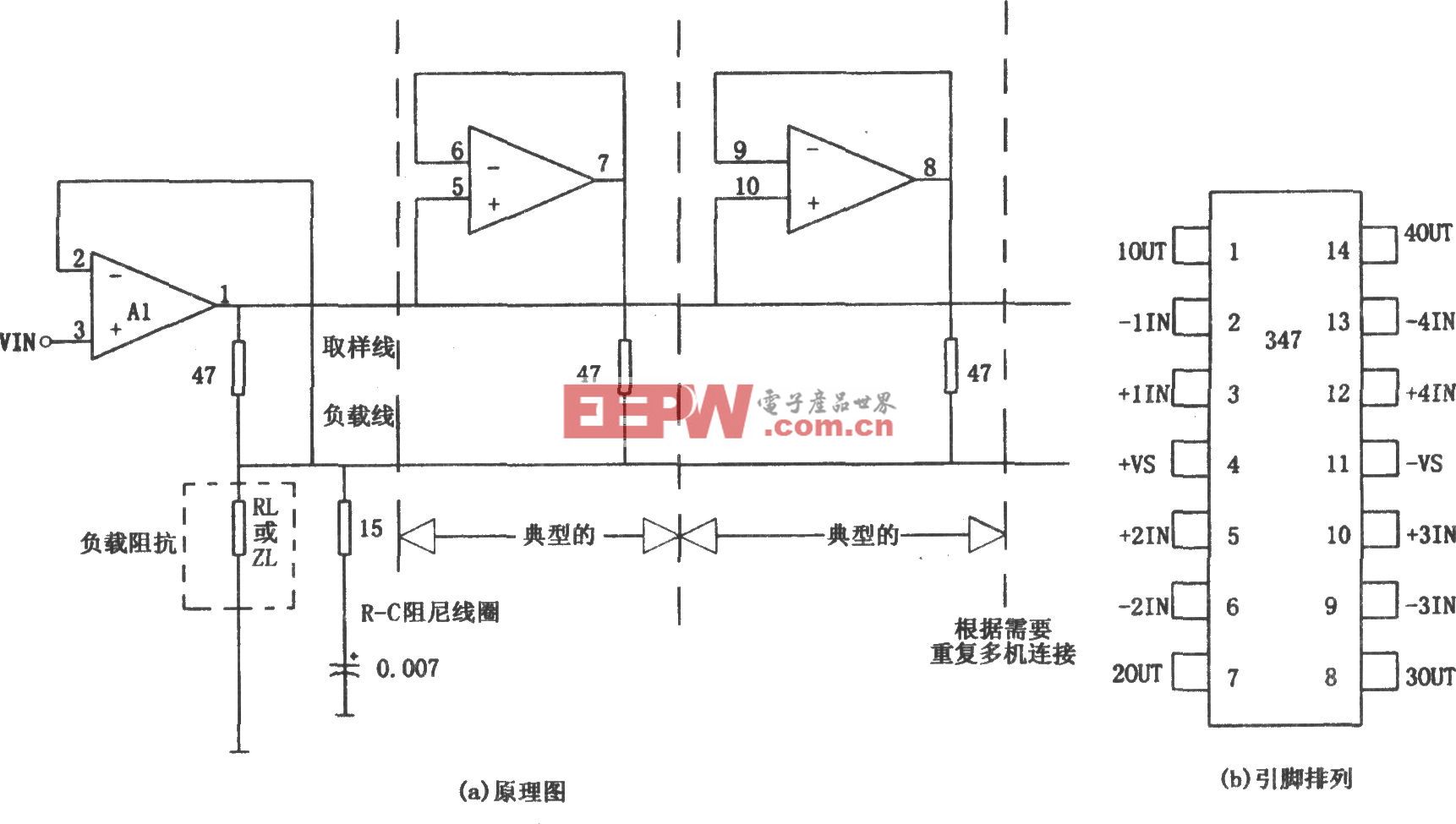

本文引用地址:http://www.j9360.com/article/201610/308048.htmPCA9605是一種單片CMOS集成電路,可在包括I2C總線的應用中實現總線緩沖功能。該緩沖器可以通過緩沖驅動SCL和SDA線來擴展總線負載,緩沖器兩側可達到最大允許的總線電容。在其最基本的實現中,該緩沖器允許擴展數量的從器件連接到一個主器件。在本例設計中,主器件是PIC的微控制器[2],從器件是兩個數據轉換器,其中一個是模數轉換器,另一個是數模轉換器。PCA9605的方向引腳(DIR)固定接地,因為時鐘由主器件提供(單向時鐘模式)。圖1給出了總的原理圖。

U2 ADC捕獲來自信號發生器的模擬信號并轉換成數字信號,然后發送給緩沖器U3,由U3驅動后上電纜傳輸,并經U4中繼后繼續傳輸。SDA數據線需要雙向驅動,從U3到U4以及U4到U3。最終由U5 ADC產生數字化后的信號。如果需要經過更長距離的電纜傳輸,可以在電路中間插入另一個緩沖器進行擴展。這種方法可以覆蓋長達數百米的有線傳輸距離[3]。

圖1:用擴展I2C總線連接兩個節點的電路原理圖。

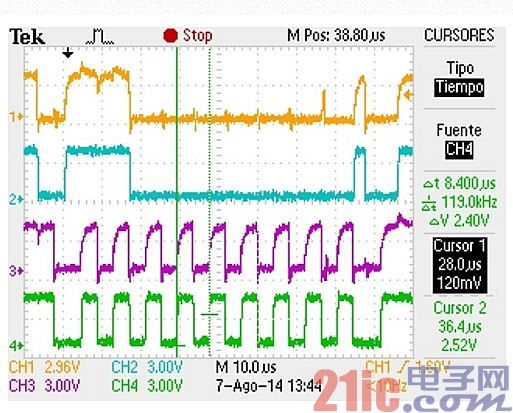

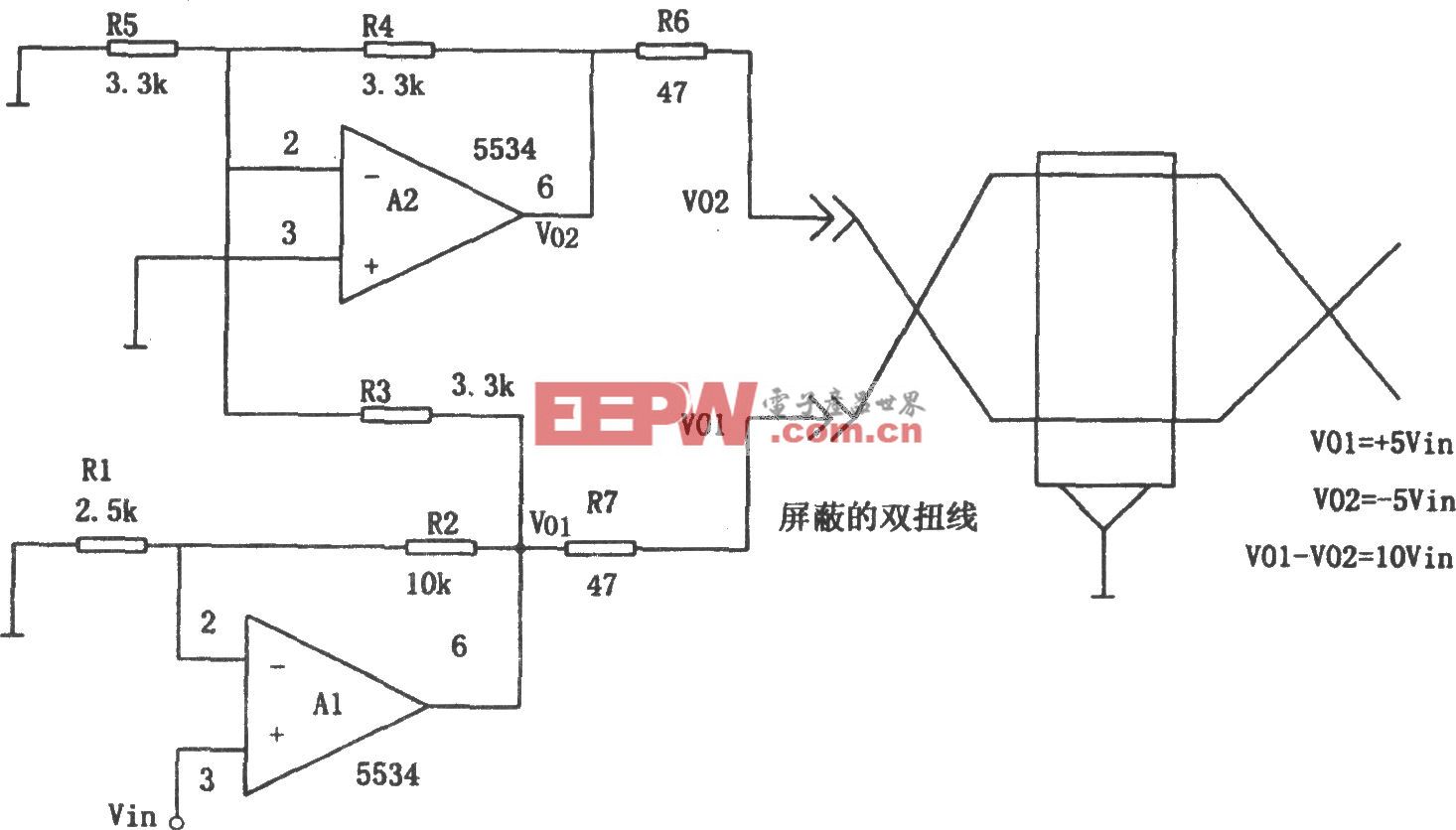

圖2顯示了通過電纜總線以125kHz速率傳輸DAC地址(0xC0)。通道1連接的是總線側SDA線(U4的引腳6),該信號通過緩沖器驅動后可消除毛刺和來自時鐘線的容性干擾以及由于使用上拉電阻的開路集成極和走線電容引起的RC效應。通道2顯示的是經過緩沖器驅動后的SDA數據信號(U4的引腳7),通道4(U4的引腳2)是經過驅動后的時鐘SCL。電纜上的時鐘信號(U4的引腳3)示于通道3,通道4是經過緩沖器驅動后的信號(U4的引腳2)。

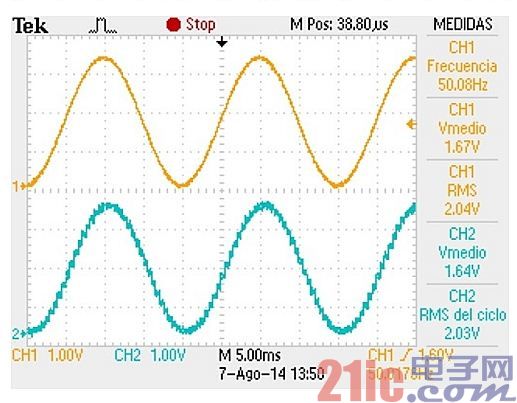

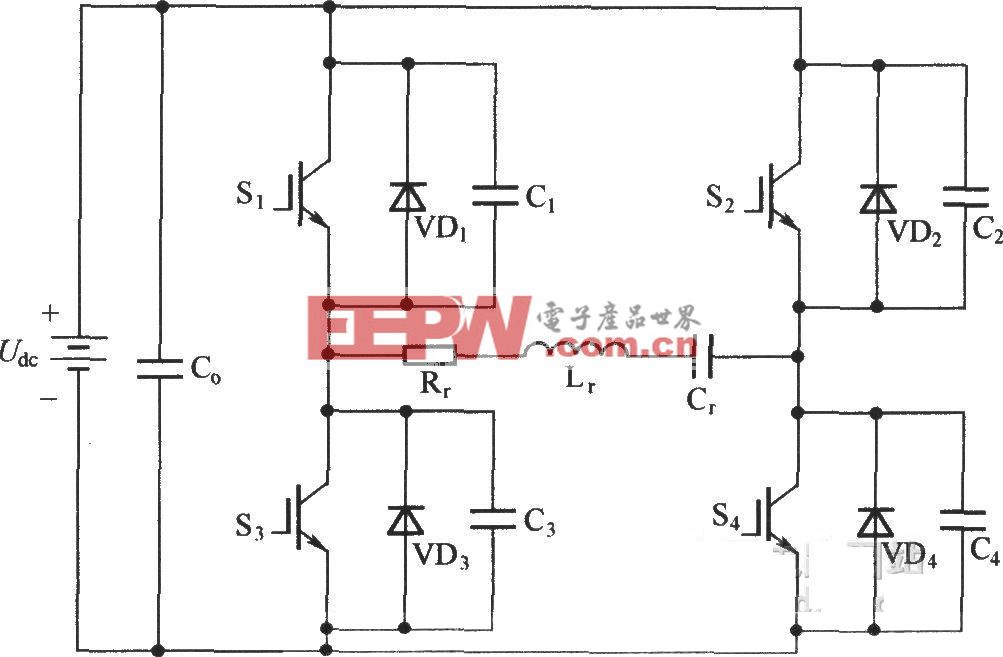

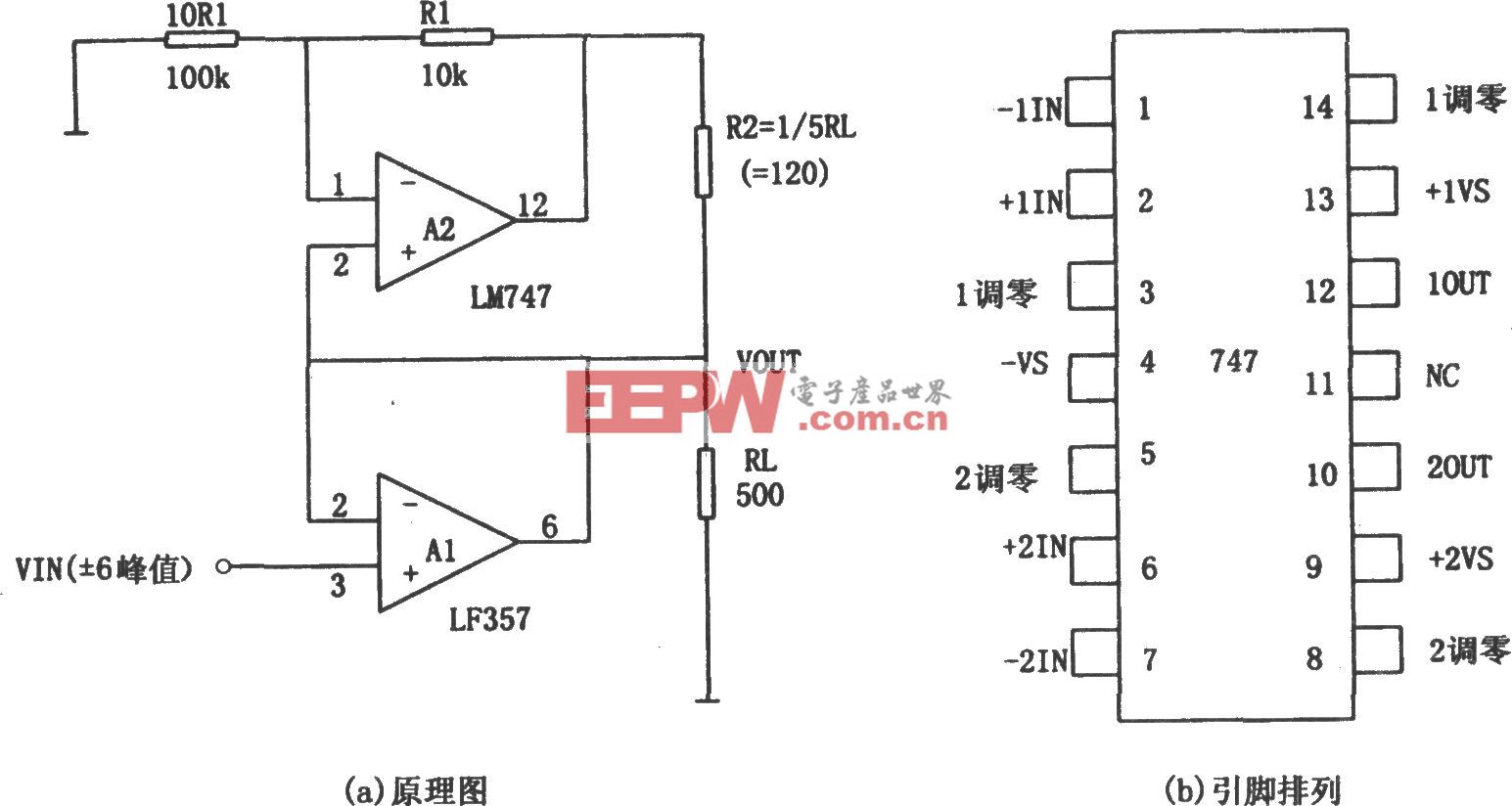

如果系統測試時給ADC U2發送一個電壓幅度為滿輸入刻度的單極性模擬信號,在DAC U5的輸出負載上就可以得到圖3所示的波形。本設計充分利用了ADC和DAC電路的特性,允許它們處理軌到軌信號。這種低頻信號可以通過在DAC輸出端增加一個低通濾波器加以改進,因為低通濾波器可以降低采樣和重構噪聲。

圖2:緩沖器前后的從節點信號。

圖3:通過I2C發送的滿刻度輸入正弦信號。

評論