一種鎖定相位編程可調全數字鎖相環設計

1 引 言

本文引用地址:http://www.j9360.com/article/201610/307961.htm鎖相技術在信號處理、調制解調、時鐘同步、倍頻、頻率綜合等領域都得到了廣泛的應用。目前鎖相技術的實現主要有模擬鎖相環(APLL)、全數字鎖相環(DPLL)、模擬數字混合鎖相環與延遲鎖相環(DLL)四種。全數字鎖相環(DPLL)具有精度高且不受溫度和電壓影響,環路帶寬和中心頻率編程可調等優點.得到了廣泛應用。

經典全數字鎖相環路由數字鑒相器、K模可逆計數器、脈沖加減控制電路和N分頻器4部分組成。在輸入信號頻率穩定條件下,鎖相環鎖定時輸出信號與輸入信號正交。在通信和其他很多應用領域,不僅需要輸出信號與輸入信號保持正交關系,有時也需要他們保持某些特定的相位差。本文在經典結構基礎上稍做改進,提出了一種輸出信號與輸入信號的鎖定相位編程可調的全數字鎖相環路的設計。經過計算機仿真分析、FPGA實現及板級系統實驗,證明了系統的可行性和可靠性。

2 經典數字鎖相環路結構及工作原理

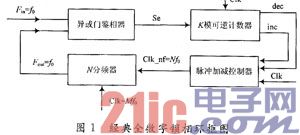

圖1示出了采用異或門鑒相器的經典數字鎖相環路的結構框圖。各個模塊的結構和功能如下:

2.1 異或門鑒相器

異或門鑒相器將鎖相環路輸入信號Fin與輸出信號Fout做減法,輸出相位差Se作為K模可逆計數器的計數方向信號。當環路鎖定時輸出信號與輸入信號穩定正交,Se是一占空比為50%的方波信號。

2.2 K模可逆計數器

K模可逆計數器產生進位和借位脈沖并起到環路濾波的作用。他由系統時鐘Clk(頻率M?0)控制對異或門鑒相器輸出的相位差信號Se進行采樣計數,當Se為低電平時做加計數,計數值達到預定模值K時輸出進位脈沖inc同時計數器回零;當Se為高電平時做減計數,計數值為零時輸出借位脈沖dec同時計數器置K。當環路鎖定Se是一占空比為50%的方波信號時,交替輸出進位和借位脈沖。計數器模值K的大小決定了環路進入鎖定的時間,K值越大環路鎖定時間越長。

2.3 脈沖加減控制器和N分頻器

脈沖加減控制器實現數字壓控振蕩器的功能。當K模可逆計數器有進位脈沖輸出時,控制器捕獲該脈沖信號,并在輸出信號Clk_nf中插入一個系統時鐘周期的脈沖,N分頻器對Clk_nf信號分頻,從而使環路輸出信號Fout超前一個時鐘周期的相位;同樣的,當有借位脈沖時控制器在Clk_nf減去一個系統時鐘周期的脈沖,從而使輸出信號Fout滯后一個時鐘周期,這樣就起到了相位調節的作用。當環路鎖定時交替出現的進位和借位脈沖調相作用相互抵消,輸出時鐘Fout 穩定。

3 改進的數宇鎖相環結構及工作原理

3.1 改進的數字鎖相環設計思路及其結構

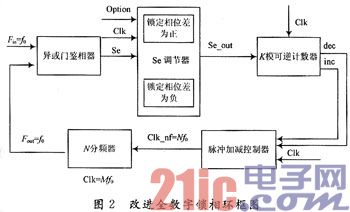

如圖2所示,在異或門鑒相器與K模可逆計數器之間插入一個Se的調節器對Se的波形進行調節,即給了K模計數器一個虛假的輸出信號與輸入信號的相位差Se_out。當偽相位差信號Se_out為方波時輸出與輸入信號鎖定在一個特定的相位。

3.2 Se調節器的設計實現

我們假定輸出信號Fout與輸入信號Fin正交時二者相差為零。設輸出信號滯后于輸入信號環路鎖定相位羞為負,輸出信號超前于輸入信號環路鎖定相位差為正。用Option信號選擇鎖定方式并輸入相位差值。分別分析鎖定相位差為負和鎖定相位差為正環路進入鎖定時各個信號之間的相位關系,很直觀地得到Se調節器的實現方法。

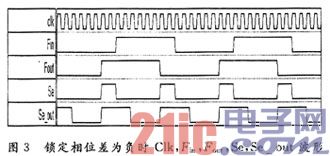

3.2.1 鎖定相位差為負Se調節器的設計實現

系統時鐘Clk,輸入信號Fin、輸出信號Fout,相位差信號Se與偽相位差信號Se_out的相位關系如圖3所示。偽相位差信號Se_out為一占空比為50%的方波,系統鎖定。此時輸出信號滯后于輸入信號一定的相位,記為off-set。相位差信號Se高電平占空比低于偽相位差信號Se_out高電平占空比的值就是輸出信號滯后于輸人信號的相位offset。Se調節器要完成的工作就是將Se調整為Se_out的波形,即將Se為低電平寬度為offset的區域轉換成高電平。具體實現為:設計一個預置值為offset的計數器。在Se為高電平時Se保持不變,同時計數器計數值保持為O,在Se由高電平變為低電平后開始加計數,當計數值未達到預置值offset。時Se仍保持為高電平,當計數值超過預置值offset時,將Se置低電平,這樣得到的波形就是所需要的se_out。

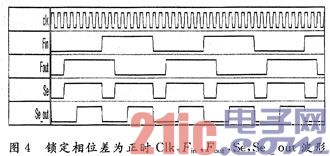

3.2.2 鎖定相位差為正Se調節器的設計實現

系統時鐘Clk、輸入信號Fin,輸出信號Fout,相位差信號Se與偽相位差信號Se_out的相位關系如圖4所示。與輸出信號滯后于輸人信號環路鎖定類似:設計一個預置值為offset的計數器。在Se為低電平時Se保持不變,同時計數器計數值保持為O,在Se由低電平變為高電平后開始加計數,當計數值未達到預置值offset時Se仍保持為低電平,當計數值超過預置值offset時,將Se置高電平,這樣得到的波形就是所需要的Se_out。

3.3 Se調節器性能分析

鎖相環開始工作時,輸出信號是落后于輸入信號的,對輸出信號Fout的相位不斷調整是在系統時鐘控制下對相位差信號Se為高電平部分逐漸加寬的過程。不同的Se調節器對此過程的響應性能不同。又系統時鐘Clk與輸入信號Fin之間的相位關系決定了輸出信號與輸入信號的鎖定誤差,Se調節器存在固有誤差。

3.3.1 鎖定相位差為負的Se調節器

鎖定相位差為負的Se調節器本身就是對Se為高電平不斷加寬,工作過程中計數器對Se為低電平計數總可以達到滿足offset,進而對Se out進行調整。系統時鐘Clk與輸入信號Fin偽同相(Fin二升沿與Clk上升沿同步)時,環路鎖定存在半個系統時鐘周期的系統固有誤差;Clk與Fin偽反相(Fin上升沿與Clk下降沿同步)時,環路鎖定不存在系統固有誤差。

3.3.2 鎖定相位差為正的Se調節

鎖定相位差為正的Se調節器本身是對Se為高電平部分不斷減少,而實際的調節是將其不段加寬,在一定時間內Se_out保持為低電平,系統時鐘Clk在此結構下造成的系統固有誤差均為正向。Clk與Fin偽同相時存在一個系統時鐘周期的系統固有誤差,CIk與Fin偽反相時存在半個系統時鐘周期的系統固有誤差。將內部將計數器的預置值設為offset減1,則系統最大固有誤差降為半個系統時鐘周期。

4 計算機仿真與FPGA實現

4.1 計算機仿真

設計采用Verilog硬件描述語言,在Mentor Graphics公司的FPGA設計平臺FPGA Advantage with PS 7.1上進行了設計、綜合及仿真,仿真器為Modelsim 6.1a。

圖5和圖6分別示出了系統時鐘Clk與輸入信號Fin偽反相,可逆計數器K值為10,分頻數N為16,鎖定相差為負3和正3時環路鎖定的過程。可以看出,Se的調節都時將Se為高電平部分逐漸展寬的過程。鎖定相差為負3時誤差為0,由于汁數器補償的作用,鎖定相位差為正3時誤差也為0。

4.2 FPGA實現及板級系統實驗

設計采用Xilinx公司的ISE 7.1i開發環境和Spar-tan3 xc3s400-4pq208 FPGA進行了實現,并在板級系統上搭建了實驗環境,用數字示波器進行了波形測試,系統工作穩定,達到了設計要求。

5 結 語

設計對經典全數字鎖相環路進行改進,通過增加相位差調節器的方法實現輸出信號與輸入信號的多相位鎖定。采用Verilog語言對整個設計進行了描述,進行了計算機仿真、FPGA實現和板級系統實驗,實現了鎖定相位編程可調的全數字鎖相環路,完成了設計目標。

評論