基于SMS4的加密通信可編程片上系統設計實現

摘要 針對面向工業用、商用以及民用電子設備加密串行通信需求,通過基于SMS4的加密通信SOPC軟硬件架構、SMSd加密通信控制器IP技術、SMS4加密通信軟件技術等內容的研究,實現了基于SMS4加密算法的串行通信技術,并在非128位明文的加密傳輸數據控制和基于8位異步模式的128位數據串行收發上效率明顯提升。基于SMS4的加密通信SOPC提高了系統的加密通信功能可定制能力,且使加密通信核心算法自主可控。

本文引用地址:http://www.j9360.com/article/201610/306411.htm串行通信是商用、民用及工業控制用電子系統廣泛使用的一種通信方式,多種電子系統通過串行通信接口傳輸敏感數據,如無線電通信設備、IC卡刷卡機等,為保證數據傳輸安全,對串行通信數據加密是必要的技術手段。SOPC技術是百萬門級大規模FPGA出現后新興的電子系統設計技術,實現的電子系統具備集成度高、功能可配置、性能可伸縮和資源可重構的特點。因此,采用SOPC技術設計加密通信系統具備良好的應用推廣價值。

分組密碼算法是大量數據加密存儲與傳輸的主要密碼算法,SMS4算法是我國官方公布的第一個商用分組對稱密碼算法,為發展自主可控的信息安全技術,應該將SMS4算法作為串行通信核心密碼算法的重要選擇。由于SMS4算法提出較晚,目前尚未有采用SMS4算法進行加密通信SOPC設計的成果出現。為使信息安全技術自主可控,優化加密通信系統設計,提高系統的加密通信功能可定制能力,因此有必要開展基于SMS4的加密通信SOPC研究與設計。

分組密碼算法具有速度快、易于標準化和便于軟硬件實現等特點,通常是信息網絡安全中實現數據加解密的核心體制,其在計算機通信和信息系統安全領域有著廣泛的應用,如國外發布的DES算法、AES算法、NESSIE算法等。2006年1月,我國國家商用密碼管理辦公室公布了SMS4分組密碼算法標準,用于保護無線局域網產品的數據安全,并被WAPI標準采納作為其中的分組密碼算法。2007年12月,在國家密碼管理局公布的《可信計算密碼支撐平臺功能與接口規范》中,SMS4算法被規定為可信密碼模塊(TCM)中要求實現的對稱密碼算法。

SMS4是一個分組對稱密碼算法,分組長度和密鑰長度為128 bit。加密算法與密鑰擴展算法均采用32輪非線性迭代結構。其中非線性變換所使用的S盒是一個具有很好密碼學特性的、由8 bit輸入產生8 bit輸出的置換。但不存在永遠安全的密碼算法。SMS4設計靈活,其中所采用的S盒可靈活地被替換,以應對突發性的安全威脅。

1 基于SMS4的加密通信原理

SMS4密碼算法是一種128位數據輸入輸出的加解密算法,輸入數據需經過32輪的函數運算才能得到輸出結果,存在較大的首個數據輸出潛伏延遲,而一旦進入連續輸出,通過硬件流水線設計可達到較高的吞吐率。串行通信控制器是一種典型的中低速通信設備,由于受到串/并轉換、波特率除數分頻、16分頻收發等設計的影響,串行通信速率不可能有較大提升。因此,SMS4算法和串行通信之間存在明顯的吞吐量不匹配問題。

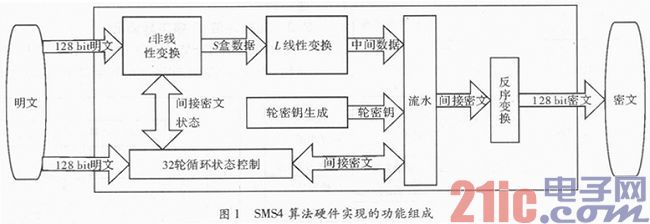

通過研究SMS4密碼算法32輪迭代運算、輪密鑰運算的運算特點,并分析全流水、全循環、循環與流水結合、單引擎、多引擎等硬件運算結構,提出合適的運算結構作為算法的基礎實現結構,以輪函數內部分級流水、節拍同步作為進一步優化的手段,突破面向串行通信的SMS4算法硬件實現優化技術,使該算法邏輯占用較少的FPGA內部資源,并使其算法的運算速度能盡量接近串行通信速率,最終達到資源占用與運

算性能的平衡。該算法硬件實現的功能組成如圖1所示。

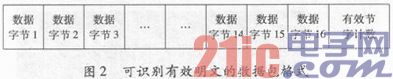

串行通信過程中,最小的數據收發單元為8位數據,即1 Byte。對128位SMS4加密運算而言,輸入的明文數據可能不是128位數據,而是1~7 Byte,無法直接完成明文的SMS4加密運算。在128位密文發送過程中,若對應明文不是128位的,還需嵌入字節計數值來標識有效數據長度,而字節計數值和有效數據難以區分。在密文接收與SMS4解密過程中,也存在得到字節計數值與有效明文提取的問題。如圖2所示。數據包具備16 Byte的數據段和1 Byte的有效字節計數值,通過有效字節計數值識別數據段中的有效數據,而其他數據則為填充數據。

通過分析處理器訪問8位通信控制器的特點,采取有效硬件邏輯設計延長8位明文連續寫入等待時間,盡可能具備128位明文輸入。通過字節自動填充將非128位明文輸入補滿到128位,實現明文的128位SMS4加密運算。將有效數據/字節計數值混合編碼,實現非128位明文對應密文的發送、接收、解密與填充字節去除。通過以上技術手段,突破非128位明文的加密傳輸數據控制技術,使處理器始終按8位明文數據訪問SMS4加密通信控制器,屏蔽128位加解密過程,具備非128位明文的加密傳輸數據控制過程對處理器透明、兼容通用串行傳輸協議、處理器加密通信負載小等特點。

一般的串行通信控制器以8位數據進行收發,當進行128位密文傳輸時,存在數據發送接口、數據接收接口、接收線狀態接口設計的位寬不匹配問題。通過設計128位寬發送數據FIFO、128位寬接收數據FIFO、128位區間接收線狀態FIFO,緩沖128位密文數據和相應的接收線狀態;通過128位/8位收發匹配邏輯,實現發送數據的128位/8位轉換、接收數據的8位/128位轉換、連續16 Byte的接收線狀態組合譯碼;通過以上技術手段,突破基于8位異步模式的128位數據串行收發技術,使128位密文串行收發無需軟件干預,故進一步降低了處理器的通信接口處理負載。

2 基于SMS4的加密通信實現

2.1 SMS4加密通信控制器IP技術

SMS4加密通信控制器IP功能組成如圖3所示,分為8位串行收發功能邏輯、128位收發邏輯、面向串行通信的SMS4算法邏輯、非128位明文的加密傳輸數據控制邏輯和處理器訪問接口邏輯。SMS4加密通信控制器IP對外提供8位數據位寬的處理器訪問接口和8位串行收發數據接口,并兼容通用串行傳輸協議,將128位SMS4密碼運算隱藏在IP內部。

8位串行收發功能邏輯提供8位數據收發、接收線狀態檢測、MODEM線控制與線狀態檢測功能。128位收發邏輯使128位SMS4密文和8位串行收發數據之間的傳輸能夠平滑、順暢地進行。面向串行通信的SMS4算法邏輯在完成128位SMS4加解密運算的同時,還具備FPGA資源利用少、加解密吞吐量與串行通信吞吐量匹配的特點。非128位明文的加密傳輸數據控制邏輯重點解決非128位明文的加解密運算和串行傳輸問題。處理器訪問接口邏輯為處理器提供8位數據位寬的訪問接口,使處理器對SMS4加密通信控制器IP的訪問方式盡可能地接近于一般的8位串行通信控制器。

2.2 加密通信IP核仿真驗證

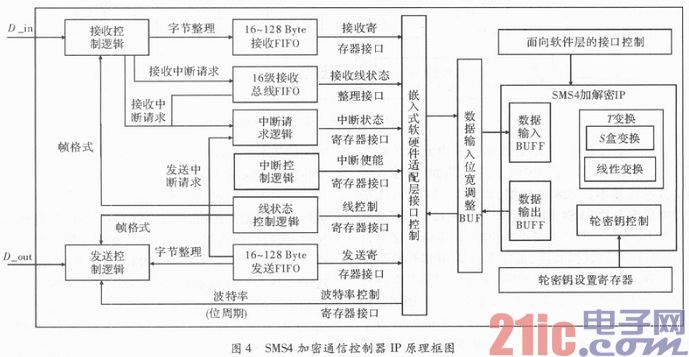

本文設計了SMS4加密通信控制器IP核完成加密通信,圖4為SMS4加密通信控制器IP的原理框圖。

采用Altera公司的Quartus II FPGA開發工具完成SMS4加密通信控制器IP的HDL代碼編譯。

使用ISim仿真器進行SMS4加密通信控制器數據接收與發送仿真,得到仿真波形,如圖5和圖6所示。SMS4加密通信控制器IP對加密算法、數據收發、數據緩沖、接收線狀態等功能進行了模塊化設計,各個模塊既相對獨立又有機組合,可完成各自功能,不同模塊之間進行數據和信號的交換實現時序控制、信息交互,從仿真結果可看出,SMS4加密通信控制器IP在不影響通信吞吐量的情況下,實現了數據的SMS4的加解密處理。

如圖5所示,SMS4加密通信控制器IP接收數據通過信號wb_cyc_i作為計數器,每接收一個有效數據,產生一次脈沖。we_sel_i表示接收控制器片選信號,在接收期間保持為高;wb_adr_i表示數據地址,wb_dat_i則表示接收數據值。

如圖6所示,SMS4加密通信控制器IP接收數據通過信號wb_cyc_i作為計數器,每接收一個有效數據,產生一次脈沖;we_sel_is表示發送控制器片選信號,在發送數據期間保持為低。wb_adr_i表示數據地址,wb_dat_i表示接收數據值。

面向串行通信的SMS4算法邏輯設計,并已集成到SMS4加密通信控制器IP中。使用ISim仿真器對SMS4算法邏輯的Verilog代碼進行波形仿真,輸入128bit數據,進行加解密,其仿真波形如圖7所示。

從圖中可看出,SMS4加密IP利用points計算通信量,圖7的通信量為1 024bit,data_in表示輸入加密數據,addr_wr表示加密過程中的地址轉換;data表示輸出解密后的密文。

2.3 基于SMS4的加密通信SOPC軟硬件架構

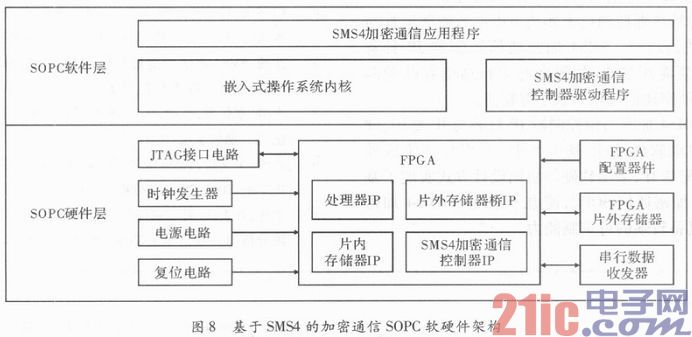

基于SMS4的加密通信SOPC軟硬件架構如圖8所示,分為SOPC硬件層和SOPC軟件層。SOPC硬件層由電源、復位、時鐘、JTAG接口、FPGA、配置器件、存儲器、串行數據收發器等電路組成,其中FPGA是核心器件,內部集成了處理器IP、存儲器及橋IP、SMS4加密通信控制器IP等。 SOPC軟件層主要南嵌入式操作系統內核、SMS4加密通信控制器驅動程序、SMS4加密通信應用程序等部分組成。

SOPC硬件功能方面,電源電路、復位電路、時鐘發生器為SOPC提供必須的電源供應、上電和硬件復位信號、時鐘同步信號。JTAG接口電路用于調試SOPC的硬件邏輯和軟件程序,同時也用于在線下載FPGA配置文件。FPGA配置器件存儲FPGA靜態配置,在上電時自動對FPGA進行配置;由于FPGA內部存儲資源有限,需外擴RAM、Flash等片外存儲器。串行數據收發器實現TTL電氣接口信號與RS-232/422電氣接口信號的轉換,使串行數據收發信號能適應遠距離傳輸環境。

SOPC軟件功能方面,嵌入式操作系統內核提供基本的存儲管理、設備管理、中斷管理及任務調度等功能。SMS4加密通信控制器驅動程序將SMS4加密通信控制器抽象成一個以文件方式訪問的設備,供應用程序調用。SMS4加密通信應用程序實現明文數據的收發,由于SMS4加密通信控制器IP可屏蔽密文傳輸過程,應用程序中無需進行加解密處理。

基于SMS4的加密通信SOPC硬件集成,需軟件集成及性能分析。SMS4加密通信SOPC主要依靠專用串行接口擴展模塊的FPGA芯片進行硬件集成,圖9為運行于Altera公司SOPC Builder開發環境的SMS4加密通信SOPC硬件集成界面。如圖所示,SMS4加密通信SOPC集成有NiosII處理器IP、SMS4加密通信控制器IP、SRAM和Flash的存儲器控制IP等IP核,需為各IP核指定Avalon總線互連拓撲關系、時鐘路徑、數據訪問空間及中斷路由等。

3 結束語

面向串行通信優化SMS4算法的硬件實現,通過基于8位異步模式的128位數據串行收發技術實現SMS4加解密和串行通信的深度整合,通過非128位明文的加密傳輸數據控制技術實現SMS4加解密運算與處理器無關,設計的SMS4加密通信控制器IP具備FPGA邏輯資源用量小、加解密與串行通信吞吐量匹配、處理器加密通信處理負載小等特點。

通過SMS4加密通信控制器IP封裝與IP復用、硬件抽象層驅動軟件設計、基于SOPC開發環境集成處理器IP及配套IP,采用軟硬件協同設計方式實現了基于SMS4的加密通信SOPC,使電子系統的SMS4加密通信功能具備較強的可定制能力。

文中研究了基于硬件實現加密串行通信功能,防破解能力強、處理器負載輕,進而提高了應用系統串行通信的安全性,有較好的推廣應用價值。其中,核心算法采用SMS4算法,有力支撐了密碼學研究成果的本土化,為滿足國內信息安全技術的自主可控需求作出了一定貢獻。另外,文中設計的可定制SOPC,也可較好滿足各種應用的加密串行通信定制需求。

評論