STM32的二乘二取二的光通信系統設計

引言

本文引用地址:http://www.j9360.com/article/201610/306214.htm隨著軌道交通列車速度的不斷提高,對軌道交通的安全性和可靠性提出了更高的要求。而傳輸設備在軌道交通系統中起到了不可替代的作用,提高傳輸設備的安全性,對軌道交通系統起著至關重要的作用。傳輸設備的主機單元要求采用雙機熱備結構或二乘二取二結構。二乘二取二計算機聯鎖系統比雙機熱備計算機聯鎖系統具有更高的安全性。

目前,大量站間傳輸設備的CPU采用的是Intel 51系列芯片或者。x86系列PC兼容機,而ARMv7系列中Cortex—M4內核在嵌入式系統中應用更加廣泛。意法半導體公司STM32是以Cortex—M3處理器為內核的,該處理器具有門數目少、中斷延遲短、調試成本低的特點,是為要求有快速中斷響應能力的深度嵌入式應用而設計的,STM32從性能到片上資源都比原傳輸設備的CPU更具有競爭力。綜上,采用STM32作為各個板塊的CPU,重點對基于STM32的二乘二取二系統進行設計。

1 光通信傳輸設備位置及作用

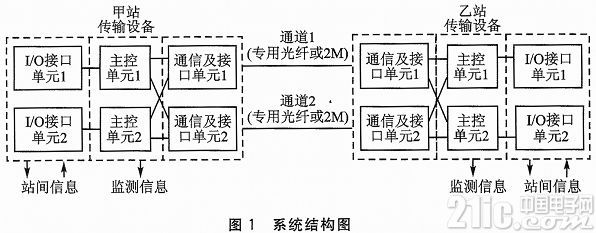

基于光通信站間安全信息傳輸設備是以計算機技術和光通信技術為基礎,利用光纖或光通道取代傳統的電纜或架空明線作為站間信息的傳輸媒介,同時采用信息安全傳輸保障技術構成的鐵路站間信息安全傳輸的專用設備。傳輸設置系統組成如圖1所示。

該設計結構應用于新傳輸設備的主控單元模塊,即圖1中主控單元1和2部分。主控單元主要完成邏輯處理和系統控制工作;通信及接口單元主要完成數據的收發;I/O接口單元要完成站間信息的采集與驅動。

2 二乘二取二安全系統設計

系統采用模塊化設計,整個系統分為5大模塊:主控板、通信板、采集驅動板、網絡接口板和電源板。其中,參與核心運算的主控板、通信板和采集驅動板采用二乘二取二結構設計,其他板采用單CPU結構。“二乘”結構中具有兩套安全相同的二取二系統,系統1為主系工作,系統2處于熱備冗余狀態。兩個系統具有完全相同的硬件結構。開機時,兩個系統同時獨立地工作。兩個系統都正常的情況下,系統1作為主系,系統輸出為系統1的輸出。如果系統1發生故障,則切換系統2為主系工作系統,系統輸出為系統2的輸出,系統1報告故障或者自動重啟。二乘系統間采用CAN總線進行通信,任意時刻系統CAN總線上只有一個CAN輸出為有效。

2.1 主控板設計

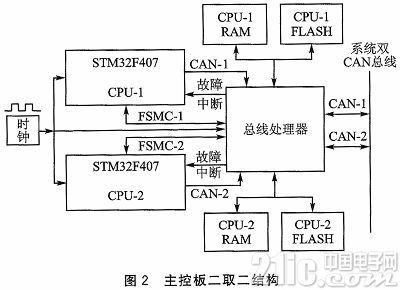

主控板作為二乘二取二系統的核心,主要完成系統的控制、繼電半自動閉塞站間、站/場間聯系等信息的處理。根據二乘二取二結構原理,由于二乘系統間的硬件與軟件完全一致,所以這里不再贅述,只給出二取二系統詳細設計。主控板的二取二結構包含兩塊STM32F407芯片作為CPU、一塊FPGA主要作為總線處理器,每個CPU有自己配套的外擴存儲器,具體結構如圖2所示。

“二取二”結構中采用兩個相同的CPU組成二取二系統,二取二系統同步方式有時鐘級同步和任務級同步。時鐘級同步主要是硬件層同步,由硬件完成2個CPU之間的同步和數據表決,包括總線上信號的比較和數據的比較,對于外部相當于只有一個CPU在運行;任務級同步主要是應用層同步,一般采用軟件完成,對每個任務的結果進行一致性比對。

主控板采用時鐘級同步,STM32F407主頻高達168MHz。STM32F407的I—Bus不僅能連接到Flash上,而且還能連接到SRAM和FSMC上,從而加快SRAM或FSMC取指令的速度。利用ST M32F407內置的雙CAN控制器,可以向總線處理器發送數據。

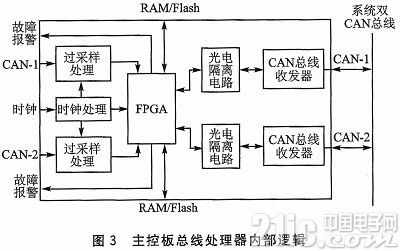

時鐘信號除了直接輸出給兩個CPU以外,還須直接供給總線處理器,其內部邏輯結構設計如圖3所示。總線處理器中時鐘處理子模塊用于產生三路時鐘信號并完成時鐘同步功能。輸出給FPGA的時鐘與CPU時鐘保持一致,輸出給過采樣處理的時鐘是系統時鐘的4倍頻。過采樣是用遠大于奈奎斯特采樣頻率的頻率對輸入信號進行采樣。本設計采用4倍過采樣法,可以提高總線的可靠性和數據恢復能力。將兩路CAN總線的輸入數據經過4倍過采樣的數據直接傳遞給FPGA,由FPGA對這8個數據進行存儲判斷,并采用多數判決規則。8個數據有5個及以上一致時,取多數的數據為待發送數據,這樣同一比特數據在總線出現不超過3處以上錯誤時,可以完成數據的正確恢復。當超過錯誤個數時,判定總線故障,FPG A向STM32F407返回故障報警信息。

2.2 通信板設計

由于通信板主要完成主控板與外部設備的通信,所以對CPU的要求沒有主控板高,CPU選用STM32F103,其主頻為72 MHz。通信板二取二結構圖與主板相似,不同處主要有兩點:

①在FPGA中嵌入一個2M生成器;

②通信板上配置E1驅動收發模塊。2M生成器用于將數據封裝為滿足于E1協議的數據報,或者將E1數據報解封裝為所需數據。這樣就省去傳統協議轉換器,減小了設備在機房的占用空間。E1驅動收發模塊用于順利收發E1數據報。

2.3 采集驅動板設計

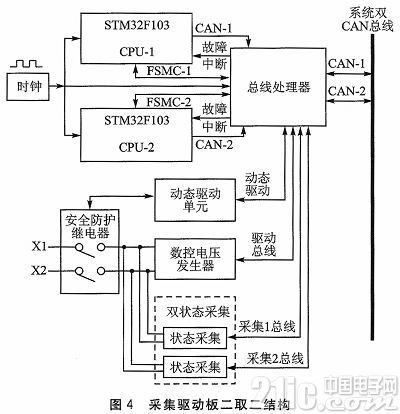

正確完整地獲取室外信號設備的數據信息是實現安全傳輸設備的重要部分,因此將采集驅動集合到一個模塊中處理,即采集驅動板模塊,其結構如圖4所示。采集驅動板結構中總線處理器與主板相似,不同之處在于FPGA還要處理動態驅動、驅動總線、采集1總線以及采集2總線。為了符合鐵路信號“故障-安全”的原則,在采集驅動板中添加動態驅動單元、數控電壓發生器、雙狀態采集。

動態驅動單元處理輸入側脈沖信號,當輸入側有脈沖信號時,輸出側給出一個具有一定驅動能力的高電平,以驅動安全型繼電器線圈,使之吸起;當輸入側沒有脈沖信號或電路發生故障時,輸出側給出一個低電平,該電平不能使繼電器吸起。這種電路一般情況下是“故障-安全”的。

因為站間距離通常是10~20 km,線損大,所以繼電器半自動電壓范圍為24~130 V。這樣設計數控電壓發生器,使其產生與外部×1和×2相匹配的不同的電壓要求。雙狀態采集主要是動態地采集FPGA和安全防護繼電器的高低電平,當有信號時,采集到一個動態的脈沖數據,當無信號時,采集到一個恒定的電平。只有采集到動態信號,設備才對信號動作,否則不響應,這樣可以做到故障導向安全。設計為雙狀態采集是為了提高設備的可靠性,將兩個狀態采集的結果輸入到總線處理器進行比較,若比較一致,則接收該采集的數據,反之,將該故障狀態報告給CPU。

采集驅動板模塊需要完成的另一重要任務是“二乘”系統間的切換功能。將“二乘”系統中的安全防護繼電器進行并聯,“二乘”系統都采集外部狀態,分別進行處理,使用串口定時進行同步通信。這樣若任意一個系統故障,另一個系統都能無縫對接。如果“二乘”系統間采集的數據不一致,則FPGA報告CPU,CPU發送同步采集請求給鄰站。鄰站收到同步采集請求返回規定的數據后,比較兩個采集數據與規定數據是否一致,判斷出故障系統。如果都不一致,則向上位機報警。

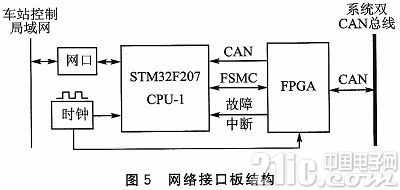

2.4 網絡接口板設計

網絡接口板完成下位機(傳輸設備)與上位機(中央網管)之間控制信息的交互,主要完成上/下位機間CAN協議與以太網協議的轉換。CPU選用STM32F207,主頻為120 MHz,它支持以太網IEEE 11588v2標準,其結構如圖5所示。

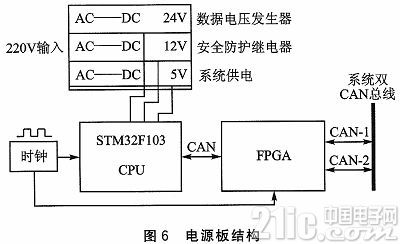

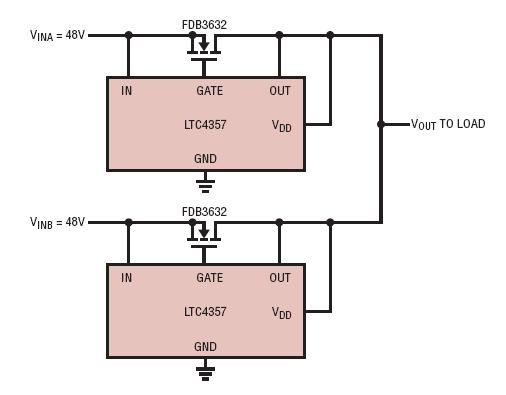

2.5 電源板

供電采用220 V市電電壓,并在220 V入口處采取電磁兼容及雷電防護措施。為了提高系統內部用電安全性,采用三種電壓分別為不同的部分供電,其結構如圖6所示。電源板不處理復雜數據,所以電源板采用STM32F103芯片作為CPU,其主要負責對各種電壓進行監測,以保證系統用電在一個安全可控的范圍內。電源板定時將系統電壓情況通過CAN總線反饋給主控板,如果出現電壓不正常,則在電源板面板上用指示燈表示,并由主控板向網管發出報警。

結語

基于Intel 51系列芯片或者x86系列PC兼容機為CPU的站間傳輸設備,從時鐘頻率和片上資源方面考慮,僅能滿足低運算量的邏輯處理,對于時鐘級同步也顯得力不從心,而STM32系列專為要求高性能、低成本、低功耗的嵌入式應用專門設計。本文提出了一種基于STM32的二乘二取二系統設計,利用不同STM32芯片滿足不同模塊的實際需求;將過采樣的概念引入到總線比較方面,提高總線信息的安全性和可靠性,為設計基于STM32的時鐘級同步二乘二取二系統提供了參考。由于實驗條件、精力和水平有限,目前該設計的某些細節還需進一步研究,系統的安全性和可靠性仍需進一步分析測試。

- STM32單片機中文官網

- STM32單片機官方開發工具

- STM32單片機參考設計

評論