基于STM32和μC/OS-II的嵌入式數字示波器設計

摘要:提出了一種基于嵌入式技術的嵌入式數字示波器設計方法,硬件設計以STM32為主控核心,采用高性能低噪聲的AD8066電壓反饋性放大器、壓控增益放大器AD603和雙路D/A轉換器TLV5618A組成程控放大電路,并采用高速帶寬A/D轉換器和IDT7204高速緩存器組成數字采集電路,以TFT彩屏輸出信號波形。軟件設計移植開源的實時操作系統μC/OS-II系統,確保了系統的實時性和穩定性。實驗結果表明設計思路正確,性能參數達到設計要求。

本文引用地址:http://www.j9360.com/article/201610/305873.htm0 引言

嵌入式數字示波器是近年來發展起來的一種集顯示、測量、運算、分析、記錄等多種功能于一體的智能化測量終端設備。憑借其強大的性能優勢,己逐步取代傳統模擬示波器。當前國內通用的數字示波器多數采用51單片機、FPGA、DSP等結構。但是51單片機處理能力有限,無法實現數字示波器的基本指標,FPGA雖然能深入開發數字示波器,然而,其成本偏高,即使加入SOPC軟核,其軟件壓力也很大。

本設計選用ARM處理器中基于Cortex-M3內核的32位STM32F103VCT6作為主控芯片。該芯片內部集成了16通道的12位高精度A/D轉換器,轉換時間僅為1μs,而且STM32芯片具省電模式,功耗低,與傳統MCU相比,其在性能和處理能力上都比較符合本設計要求。

1 系統設計方案

1.1 系統工作原理

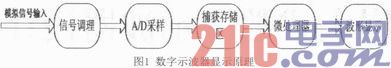

數字示波器的工作原理可以用圖1來描述,當輸入被測信號從無源探頭進入到數字示波器,首先通過的是示波器的信號調理模塊,由于后續的A/D轉換器對其測量電壓有一個規定的量程范圍,所以,示波器的信號調理模塊就是負責對輸入信號的預先處理,通過放大器放大或者通過衰減網絡衰減到一定合適的幅度,然后才進入A/D轉換器。在這一階段,微控制器可設置放大和衰減的倍數來讓用戶選擇調整信號的幅度和位置范圍。

在A/D采樣模塊階段,信號實時在離散點采樣,采樣位置的信號電壓轉換為數字值,而這些數字值成為采樣點。該處理過程稱為信號數字化。A/D采為采樣速率,表示為樣值每秒(S/s)。A/D轉換器最終將輸入信號轉換為二進制數據,傳送給捕獲存儲區。被測的模擬信號在顯示之前要通過微處理器的處理,微處理器處理信號,包括獲取信號的電壓峰峰值、有效值、周期、頻率、上升時間、相位、延遲、占空比、均方值等信息,然后調整顯示運行。最后,信號通過顯示器的顯存顯示在屏幕上。

1.2 系統設計框圖

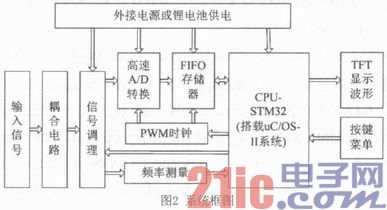

微處理器采用意法半導體的32位處理器STM32F103VET6,其內部是ARM公司的Conex—M3內核,工作主頻最高可達72MHz,再在其上面移植開源的實時操作系統C/OS—II,確保系統的實時性和穩定性。由于高速A/D轉換器的速度太快,STM32處理數據的速度跟不上,所以在中間加入FIFO高速緩存器。利用STM32內部自帶的FSMC(靈活的靜態存儲器控制器)來控制TFT液晶屏刷新波形,可實現更高頻率的信號的波形刷新和顯示。此為,利用STM32的高級定時器可輸出高達12MHz的時鐘,可以作為高速A/D轉換器的采樣時鐘和FIFO存儲器的控制時鐘,從而避免了一大堆由有源晶振和數字芯片組成的時鐘電路,系統框圖如圖2所示。

1.3 程控放大電路設計

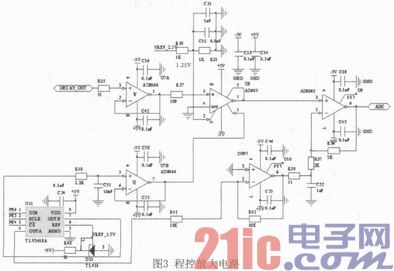

本設計的程控放大電路如圖3所示,衰減后的信號先經過的是由高性能、低噪聲的電壓反饋型放大器AD8066組成的電壓跟隨器,然后經過限流電阻R進入到壓控增益放大器AD603。AD603是ADI公司生產的低噪聲、90MHz帶寬的可變增益放大器,增益以dB為線性,經過精密校準,而且不隨溫度和電源電壓而變化。增益由高阻抗(50M Ω)、低偏置(200nA)差分輸入控制;比例因子為25mV/dB,因此僅需要1V的增益控制電壓就能覆蓋增益范圍的中間40 dB。所以改變AD603的控制電壓即可改變該器件的放大倍數。1號引腳恒定輸入1.25V電壓,2號引腳的電壓由一片D/A轉換器TLV5618A來輸出。

由于后級A/D轉換器ADS830的輸入模擬電壓范圍是1.5~3.5V,基線輸入電壓是2.5V,為了盡量利用A/D轉換器的量程,所以需要給前端輸入的模擬信號加上2.5V的偏置電壓。雙路D/A轉換器TLN5618A的另外一路輸出OUTB就是為了給輸入信號加入2.5V的偏置電壓而設計的。同樣的,為了保證這2.5V電壓的穩定,中間加入反相電壓跟隨器。

1.4 數字采集電路設計

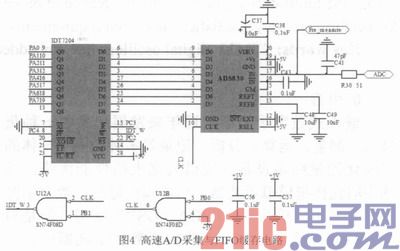

本設計的數字采集電路如圖4所示,從程控放大電路輸出的信號在進入A/D前先進入的是截止頻率為66MHz的低通濾波器,因為所用A/D轉換器ADS830的最大采樣頻率是60MHz,所以它理論上能采集到的最大信號就是60MHz,為了避免更高頻率的噪聲影響A/D轉換器工作,所以要設計這樣一個低通濾波器。A/D轉換器ADS830是德州儀器公司的一個8位分辨率高速A/D轉換器,其采樣頻率范圍是10kSa/s~60MSa/s。它的參考電壓源可選擇為內部參考和外部參考,這里為了簡化設計,選用它的內部參考電壓源。

雖然STM32主頻最高高達72MHz,但是在程序里對A/D轉換器采集回來的數據的處理速度實際上是比不上ADS830的60MHz采樣頻率的,所以為了緩沖高速數據,中間加入高速緩存器IDT7204。IDT7204是雙口的SRAM,FIFO存儲器,工作方式是不依靠地址線,隨著寫入或讀取信號來對數據指針進行遞加或遞減,來實現對數據的尋址。IDT7204的存儲深度是4K字節,有三個存儲標志,這里用到了它的“數據滿標志FF”,當微處理器STM32讀取FF標志,如果為低電平,證明FIFO存儲器已經讀取了4096個ADS830的數據,然后暫停對A/D轉換器數據的讀取。微處理器STM32處理當前存儲區的數據;等待出來完畢,再次讓IDT7204讀取ADS830的數據,如此循環即可得到當前示波器輸入信號的完整波形數據。

評論