CPS1432交換芯片的串行RapidIO互連技術

引言

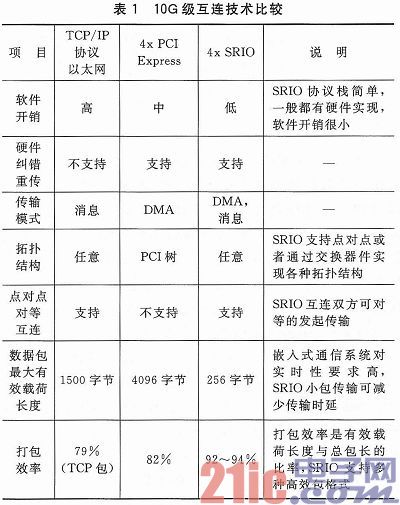

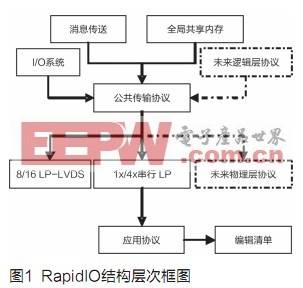

本文引用地址:http://www.j9360.com/article/201609/304015.htm串行RapidIO(SRIO)是針對嵌入式系統內部高速互連應用而設計的,數據打包效率高、傳輸時延小、協議及流控機制簡單、糾錯重傳機制和協議棧易于用硬件實現,降低了軟件復雜度,支持多種物理層技術和傳輸模式,易于擴展。SRIO引腳少、成本低,便于器件之間的互連。表1列出10G級互連技術的比較。

通過比較可以看出,SRIO可以滿足高性能嵌入式系統芯片間及板間互連對帶寬、成本、靈活性和可靠性越來越高的要求。本文介紹基于SRIO交換芯片CPS1432的高速處理系統,從總體設計、硬件設計和軟件設計3個方面介紹RapidIO互連技術方案。

1 系統設計

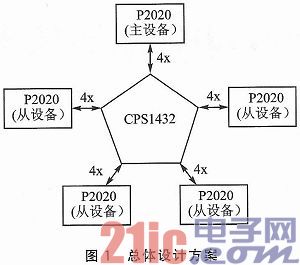

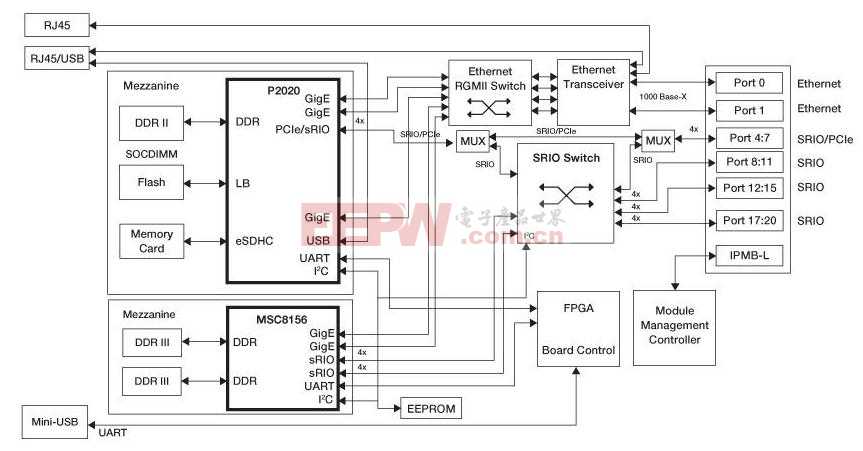

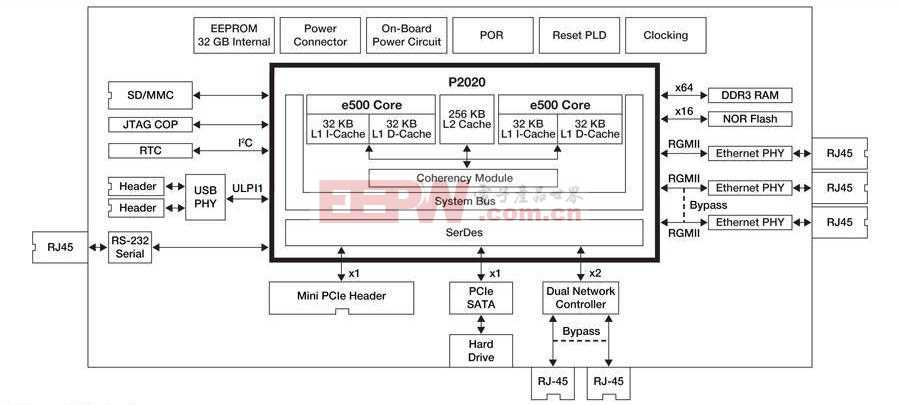

RapidIO網絡主要由終端器件(End Point)和交換器件(Switch)組成。在本方案中終端器件采用P2020型CPU,運行嵌入式Linux系統,交換器件采用CPS1432,兩者組成星型拓撲結構。總體設計方案如圖1所示。

SRIO物理層支持全雙丁傳輸和1x、2x及4x三種連接方式,采用8/10 b編碼,為了提高系統的吞吐量,本方案采用4x方式連接,理論帶寬可達到10 Gbps。整個系統的終端器件中有且只有一個ID為0的主設備,其他終端器件都是從設備。在系統初始化過程中,主設備對各個從設備進行枚舉,并為從設備分配一個非0的ID,這些ID類似于以太網中的MAC地址。在枚舉過程中,通過發送維護包,對交換器件CPS1432的各個端口進行設置,建立各個端口與終端器件的對應關系,初始化交換芯片各個端口的路由表。當整個系統枚舉完成后,終端器件發送包含目的ID的數據包,即可通過CPS1432轉發到目的終端器件的對應端口,從而實現互連互通。

2 硬件方案設計

2. 1 硬件設計

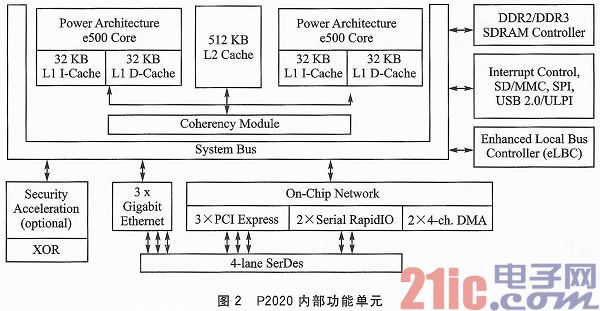

P2020是飛思卡爾公司的高性能雙核通信處理器,基于45 nm工藝,采用e500 Power Architecture核心,主頻可達1.2 GHz,對應的單核器件為P2010。兩者均集成了豐富的接口,包括SerDes、千兆以太網、PCI—Express、RapidIO以及USB等。內部4個SerDes通道可在2個SRIO端口、3個PCI-Express端口以及2個SGMII端口之間進行分配,P2020內部功能單元如圖2所示。

P2020內部集成了符合RapidIO Interconnect Specification1.2版本規范的RapidIO控制器,控制器由RapidIO端口和RapidIO消息單元(RMU)組成。P2020的2個SRIO端口都支持1x或4x的物理鏈路,單條SerDes鏈路最大支持3.125 Gbps的波特率,4x端口理論峰值帶寬為10 Gbps。消息傳遞單元支持2個數據消息發送控制器(outbound nlessage contro ller)、2個數據消息接收控制器(inbound message controller)、1個門鈴消息發送控制器(outbound doorbell controller)、1個門鈴消息接收控制器(inbound doorbell cont roller)以及1個端口寫接收控制器(inbound port—write controller)。消息傳遞單元支持3種操作模式:直接模式(Direct model)、隊列模式(Chainingmodel)和多播模式(Mul ticast model)。支持硬件的錯誤檢查和重發機制,減輕了CPU的負擔。

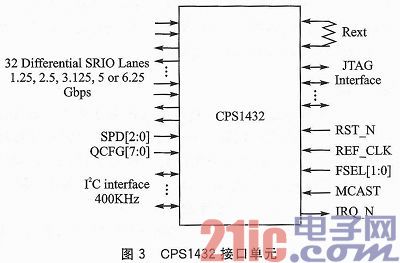

CPS1432是IDT公司的RapidIO交換芯片,基于RapidIO 2.1規范(向下兼容),共有32路串行通道,可以靈活配置為8個4x,14個2x,14個1x的端口工作方式,端口速率最大支持到6.25 Gbps,芯片內部交換帶寬達到160 Gbps,廣泛地應用于板內及板間芯片的RapidIO互連。該芯片支持上電配置引腳來進行配置,也可以通過SRIO、I2C總線或JTAG接口直接操作內部寄存器,同時I2C總線接口支持主模式,可從外部I2C EPROM中直接讀取配置數據,其接口單元如圖3所示。

為了便于配置不同的模式,本系統將P2020和CPS1432的配置引腳都引入了FPGA,CPS1432的I2C總線接口連接到板載CPU的I2C總線接口上,由CPU進行內部寄存器的讀寫控制。上電復位時,通過P2020的配置引腳cfg_IO_ports[0:3]將4個SerDes通道配置為一個4x的SRIO端口,速率3.125 Gbps,根據芯片要求,Serdes參考時鐘應選擇125 MHz。通過CP S1432的配置引腳QCFG[7:0]和SPD[2:0]將32路串行鏈路配置為8個4x的SRIO端口,速率均為3.125 Gbps。

2.2 注意事項

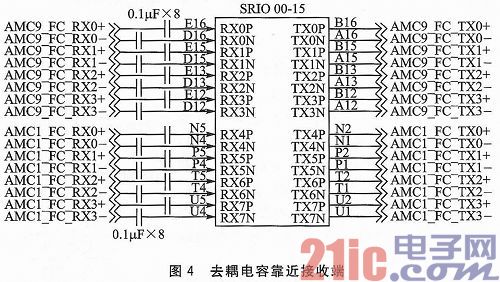

在電路設計上,由于SRIO引腳數量少,互連相對簡單。收發信號之間采用交流耦合方式,在數據接收端串接0.1μF的去耦電容,如圖4所示。電容推薦采用0402封裝,布局上靠近芯片接收端引腳放置,且4個通道的耦合電容與芯片引腳之間的走線等長。

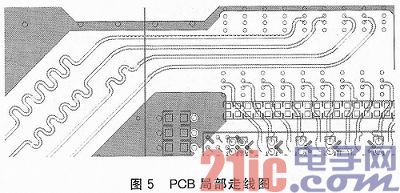

在PCB設計方面,基于信號完整性的考慮,需注意以下幾點:

①對于常用的FR4板材,要注意疊層和走線的線寬,滿足差分阻抗100Ω;

②差分線對內要求嚴格等長,由于SRIO收發信號獨立,對于2x或4x的鏈路,收發各自的差分對之間也要做等長處理(本系統要求相差10 mil以內);

③盡量全直線走線,需要彎折的地方,采用圓弧轉折;

④使用中間層走線,避免頂層和底層,且走線外圍做包地處理;

⑤盡量不要超過3個過孔(不包括BGA發送端的扇出過孔),信號換層時,要在換層的過孔兩側添加用于回流的地孔。

圖5是本系統中的CPS1432芯片外圍的局部走線圖。

評論