基于變換采樣的超寬帶接收機設計

在高精度UWB定位系統中,目標信號是超短脈寬的脈沖,有很寬的帶寬,為了對這種寬帶信號進行處理,我們要求如下兩個條件。1)設計應該實現超高的采樣率。對于UWB定位系統,恢復較好的脈沖波形以獲得較高時間分辨率信息是非常有必要的,這就需要超高的采樣率。等效采樣率與信號重復頻率和采樣時鐘有關。2)系統應該提供足夠的模擬帶寬來處理UWB信號以防止失真。

本文引用地址:http://www.j9360.com/article/201609/303779.htm現有對UWB脈沖信號的采樣方法有3種:直接采樣、頻域采樣、順序欠采樣。對于直接采樣,由于每個ADC的輸入信號帶寬非常大,會導致ADC的采樣保持電路難于設計;ADC的采樣結果受采樣時鐘抖動影響較大,因此采樣時鐘必須達到較高的精確度;同時,當實現較高的等效采樣率時,會需要較多的ADC,資源開銷大。此外,當UWB系統受到窄帶信號干擾時,就必須提高時間交替ADC的動態范圍,來保證接收機的性能。與直接采樣相比,頻域采樣對時鐘抖動則不敏感。但是濾波器組設計復雜。順序欠采樣是通過兩個參考時鐘振蕩器來實現的。假設f0= 9.999 000 MHz,f0+△f=10 MHz,那么順序欠采樣重構一個脈沖信號所需時間為1 ms,可以達到的等效采樣率為99.99 GHz。其與需求的差距為:重構信號所需時間長,容易受到時鐘抖動的影響。

為了解決帶寬與采樣率這一矛盾,本文設計一款基于變換采樣的UWB信號接收機。通過超寬帶跟蹤保持器(帶寬為5 GHz)與低采樣率的ADC(500MSPS)配合工作可以實現帶寬為5 GHz,等效采樣率最大為200 GHz的超寬帶信號接收。該技術將為分離載荷通信與定位技術的實現提供有力的支持。

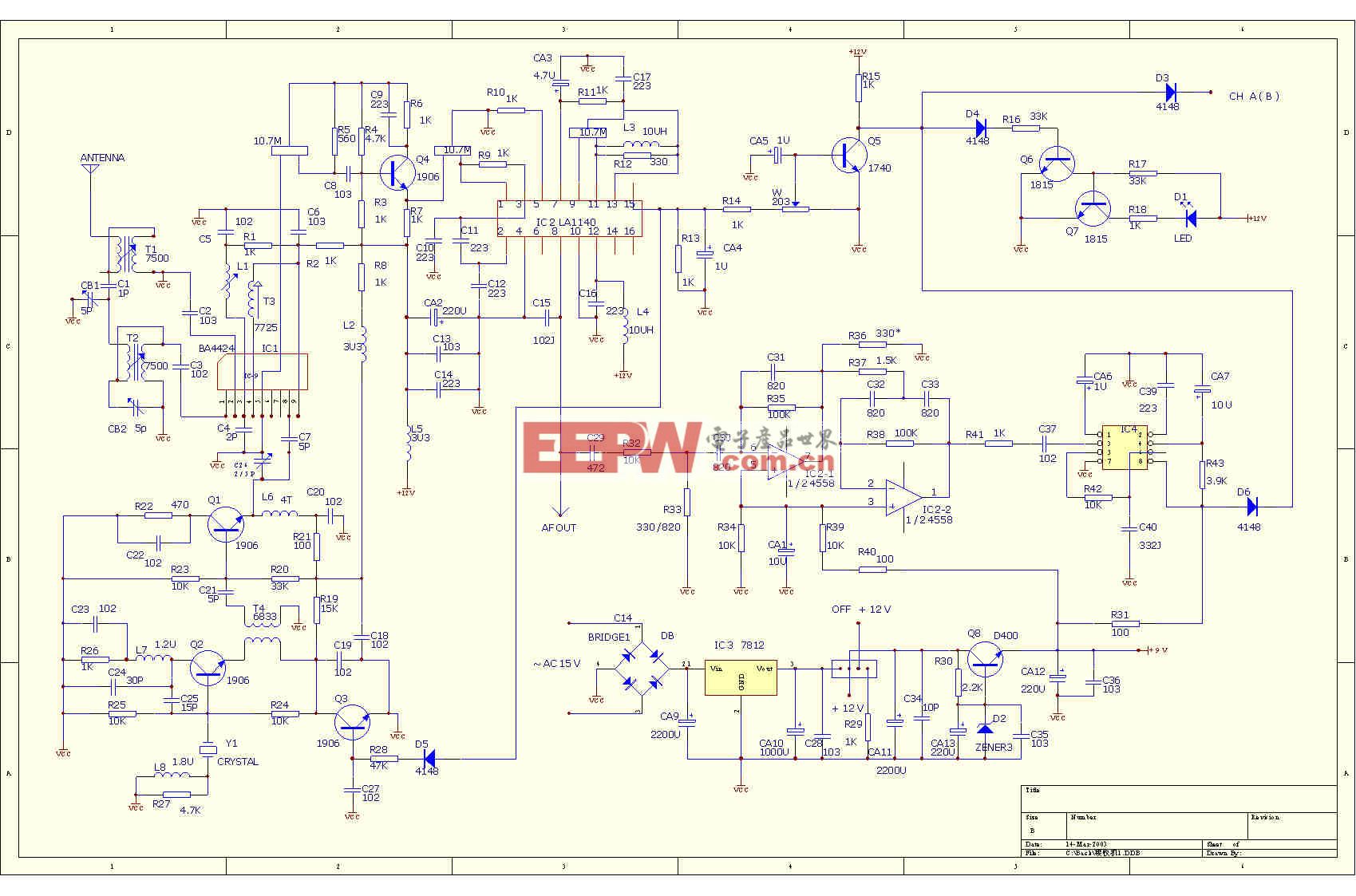

1 總體設計

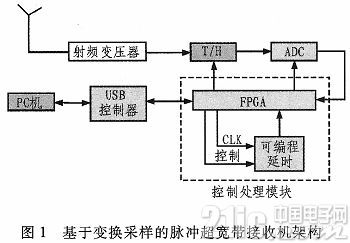

基于變換采樣的脈沖式超寬帶系統接收機架構如圖1所示。它包括一個跟蹤保持放大器、一個ADC和一個可編程延時芯片。實際的ADC有一個固有的帶寬限制,這與ADC可達到的最高采樣率有關。因為ADC的采樣率相對較低,ADC的模擬帶寬可能無法覆蓋UWB脈沖的帶寬。因此考慮在ADC之前放置一個采樣保持放大器(模擬帶寬5 GHz)以對輸入的帶通信號進行直接采樣,可有效地將輸入信號轉化為ADC需要的低通頻率。

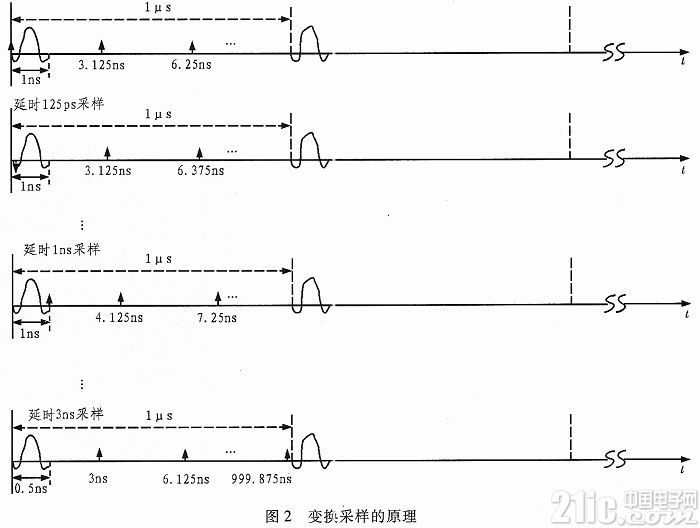

為了檢測幾百皮秒級(300 ps或3 GHz帶寬)的窄脈沖,ADC的采樣率至少為6 GS/s才能滿足奈奎斯特準則,然而這樣高性能的ADC在大多數的應用中要么是無法買到,要么是太昂貴。文中致力于解決這個問題,通過采樣時鐘產生技術、高速ADC技術和數據拼接與處理技術來實現對UWB脈沖信號的無失真采樣。超寬帶系統接收機架構中使用跟蹤保持器使變換采樣器的模擬帶寬達到了5 GHz,利用可編程延時芯片和低采樣率的ADC即可等效實現8 GS/s的采樣率。其原理框圖如圖2所示,橫軸箭頭對應的時間為采樣時刻。

發射的UWB信號重復頻率為1 MHz,其脈沖重復時間為1μs。所用的ADC采樣率為320 MS/s,那么采樣間隔為3.125 ns,而UWB脈沖寬度為1 ns。ADC首先對第一個周期的脈沖進行采樣,然后送入FPGA中存儲,然后在下一個脈沖周期延時125 ps后再對UWB脈沖信號采樣、存儲;那么經過25個周期延時24次(每次延時以125 ps遞增)即可得到25組樣本值,每組樣本選取40個采樣值。利用數據拼接與處理技術,即可得到一個UWB脈沖周期的全部信息,即可實現對脈寬為1ns的UWB信號的無失真采樣。這樣,等效采樣間隔為125 ps,即等效采樣率為8 GS/s。這種采樣方法就是以時間資源為代價來獲取8GS/S的等效采樣率。

2 系統硬件設計

該系統分為4個部分:射頻前端,ADC/時鐘配置,數字硬件以及外部接口。

2.1 射頻前端

射頻前端包括單端轉差分部分,以及跟蹤保持放大器。單端轉差分部分利用ETC1-1-13TR傳輸線變壓器進行轉換,該變壓器阻抗比為1:1,工作頻率為4.5~3 000 MHz。為了擴展高速AD轉換的模擬帶寬以及高頻線性度,在ADC之前加上HMC760LC4B跟蹤保持放大器。該放大器具有5 GHz的輸入帶寬,最大采樣率為4 GS/s。為了在采樣時鐘到來之前跟蹤保持放大器保持住數據,需要跟蹤保持放大器的采樣時鐘領先ADC采樣時鐘一個時間間隔。

2.2 ADC/時鐘配置

高速數據采集系統中,AD轉換芯片是模擬和數字的轉換中介,因此很大程度上決定了整個系統的性能。然而AD轉換的性能很大程度上又受到采樣時鐘的制約,傳統的時鐘電路都難提供高速ADC芯片所要求的低抖動、高速度的時鐘。

本采集系統中ADC芯片ADS5463要求的采樣時鐘為320 MHz的高速差分時鐘,差分形式為低電壓偽發射極耦合邏輯電平LVPECL。因此,系統對采樣時鐘的抖動十分敏感,而采用差分時鐘可以比采用單端時鐘有更好的噪聲抑制功能,同時,采用差分時鐘,可以減小時鐘的抖動,提高SNR,從而獲得更好的系統性能。本文使用FPGA內部的增強型PLL或者快速PLL對系統時鐘倍頻產生采樣時鐘,采樣時鐘最大為500 MHz。該系統采用變換采樣的原理對UWB脈沖周期信號進行采樣,需要在每一個脈沖重復周期內進行(等效采樣率的倒數)的延時。延時芯片選用sy8929 7u,該芯片為雙通道可編程延時線,每個通道的延時范圍為2~7 ns,可編程延時增量為5 ps。延時變化基于串行可編程接口(SCLK,SDATA和SLOAD),每個通道的控制字為10 bit。為了增加延時,可以將多個sy89297u串聯起來使用。

2.3 數字硬件

FPGA的并行性處理方式,使得FPGA成為高速ADC芯片高速數據流進行接收、緩存處理的理想方案,同時,這也是整個系統設計的關鍵。該系統采用芯片XC5VLX30—1FFG676I。該芯片array為,slice為4 800,最大可分配RAM為320 kb,最大高速I/O為400個,特別適合高速率大數據容量的處理。本文脈沖重復頻率為1 MHz,AD的采樣率為320MHz,那么在一個脈沖重復周期內將有320個采樣點,但是由于一個周期內脈沖的占空比較小,為了減小資源的占用,降低數據率,在每個周期內只取那些有脈沖的采樣點進行存儲。在數據進行存儲時,需要將數據進行拼接,然后再順序進行讀取。為了降低數據的速率,還需要對數據進行非相干累加,這樣就可以通過外部端口進行輸出,在這里我們選用USB端口與PC連接,通過控制上位機,可以在電腦上進行數據的分析。

評論