基于Avalon總線SHT11溫濕度傳感器自定義IP核的開發

SOPC(System On a Programmable Chip,可編程芯片系統)就是在一個可編程芯片上實現一個電子系統的技術。SOPC是可編程邏輯器件技術和SoC(System on Chip)技術發展與融合的產物[1?2]。

本文引用地址:http://www.j9360.com/article/201609/303623.htmSOPC的關鍵技術之一就是IP核,也就是知識產權核。所謂的IP核就是指將一些比較復雜的功能模塊,如音頻編/解碼、SDRAM等,設計成可以修改參數的模塊,可以直接調用。實際的SOPC設計過程,用戶常常有特殊的需求,而EDA廠商未提供該IP核。所以,在設計中添加用戶自定義組件顯得特別重要。

1 Avalon總線

SOPC組件通過Avalon交換架構或者Avalon總線連接在一起,SOPC系統的可定制特性要求Avalon總線也具備靈活的可定制特性。Avalon總線是一種協議較為簡單的同步總線,有其規范及傳輸模式。

Avalon總線是由Altera公司開發的一種專用的用于連接SOPC系統組件及從組件的內部連線技術,它是由SOPC Builder自動生成,是一種理想的用于系統處理器和外設之間的內連總線。一般使用的是Avalon從端口。一個典型從端口包含的信號如表1所列。

表1 Avalon從端口信號

Avalon總線使用很少的邏輯資源支持數據總線復用、地址譯碼、產生等待周期和高級交換式總線傳輸。該總線為用戶提供非常友好的接口,屏蔽搭建系統的細節,減輕了系統搭建的工作量。

2 SHT11自定義IP核的開發

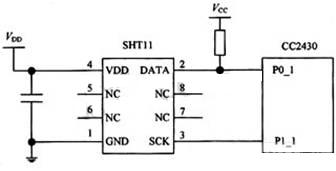

SHT11是瑞士Sensirion公司推出的SHTxx系列數字溫濕度傳感器。它是基于先進的CMOSens數字傳感技術,具有極高的可靠性和長期穩定性。全量程標定,兩線數字接口,大大縮短研發時間,簡化外圍電路并降低費用。此外,具有體積小、響應迅速、能耗低、可浸沒、抗干擾能力強、溫濕一體的特點,兼有露點測量,性價比高,使該產品能夠適于多種場合的應用。SHT11的高級功能是通過狀態寄存器來實現的[3]。

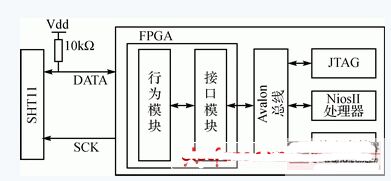

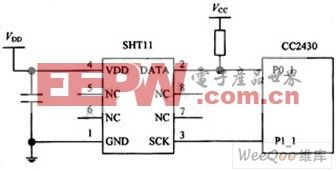

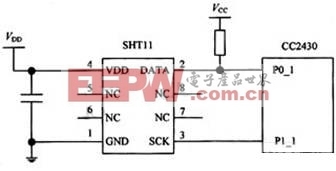

圖1為系統結構圖。由圖可知,系統主要分為接口模塊和行為模塊,行為模塊實現芯片的驅動邏輯功能,接口模塊通過內部總線和Avalon總線相連,實現了對行為模塊的控制。利用SOPC Builder建立系統,通過數據線和時鐘線來控制SHT11。其中要加上10 kΩ的上拉電阻。

圖1 系統結構圖

采用自定義IP核的方式,也就是把SHT11看成外部存儲器或者是I/O設備,將其作為從設備連接到Nios II嵌入式處理器的Avalon總線上,系統用訪問I/O設備或者是讀寫寄存器的方式對其進行控制。所以,編寫自定義IP核的時候,根據實體SHT11的時序要求,編寫驅動、接口等,靈活地控制并實現復雜的時序。其中可以按照自己的需求靈活地定義狀態、標志位、控制位等。設計完成后,獨立添加到SOPC Builder,用戶可以直接使用。該方法比單純利用PIO內核更加節省處理器的開銷,充分發揮了處理器的能力[4?6]。

2.2 接口模塊的設計

根據SHT11的描述,確定該模塊與Avalon所需要的接口信號。通過使用較少的信號來處理讀寫。系統通過時鐘線、數據線和SHT11相連,根據時鐘的時序向數據線寫命令,SHT11通過數據線輸出數據。設計模塊的輸入信號為:clk,sysclk, n_rest, data_i,data_o,wr,rd, addr。輸出信號為:SCK,DATA(DATA是雙向數據線)。端口信號的部分說明如下:

moduleSHT11(

clk,//系統時鐘

n_rest,//系統復位

data_i,//Avalon寫數據總線

data_o,//Avalon讀數據總線

wr,//Avalon寫請求

rd,//Avalon讀請求

sysclk,//系統時鐘

addr,//Avalon地址總線

SCK,//時鐘線輸出

DATA,//數據輸入輸出(雙向)

);

2.3 行為模塊的實現

行為模塊實現的是SHT11的功能。該部分是整個設計的核心,實現對SHT11的控制。設計時必須根據驅動控制的規范以及時序的要求來編寫。設計的過程中,信號的控制較為復雜,但在時序邏輯中,這又十分重要。可以設定一系列的寄存器,作為訪問硬件的通道[7?8]。

根據其驅動規范,不同的命令實現相應的功能。傳輸開始時,應該發出啟動信號。啟動信號包括時鐘線為高,數據線由高變低,并在下一個時鐘線為高的時候將數據線變高。當啟動信號開始后,輸入相應指令(包含3位地址和5位命令),通過數據線,確定接收到ACK信號后,表示SHT11已經正確接收命令。待一定的時間后,當數據線由高拉低后開始信號的傳輸。系統通過確認數據線上的ACK來確定每個字節的傳輸。數據傳輸完畢,進行CRC校驗。校驗完畢后,ACK為高,結束傳輸。

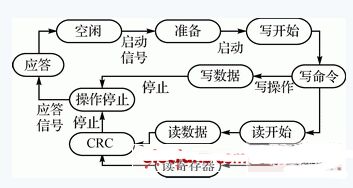

在進行設計時,采用嵌套狀態機來實現驅動邏輯。根據驅動控制器的讀寫命令及讀寫時序,采取不同狀態機來實現,如圖2所示。輸入命令之后,根據不同的讀寫請求,進入不同的狀態機。

圖2 狀態機

通過rd和wr以及地址addr控制數據線的讀寫。當addr=1wr,則向數據線寫數據(data_i),data_i 的輸入格式是crc(1位)wr_data(16位)command(2位),當addr=0wr,進入狀態機;當addr=2 amp; amp;rd,從數據線讀取數據data_o。

設內部寄存器command,根據不同的命令,進入不同的狀態機循環:若command為01,通過數據線向寄存器寫數據;若command為 10,通過數據線從寄存器讀數據;若command為其他,則讀取數據。當傳送8位數據后,需判斷雙向數據線DATA的ACK信號的高低,當接收到ACK 信號時,再根據相應的命令,進行數據的傳輸。當數據傳輸完畢后,需要經行CRC校驗。圖3是仿真時序圖,實現向寄存器寫數據的功能。

2.4 軟件設計

該部分可以直接在SOPC Builder 中添加設計好的IP核和Verilog HDL 語言描述的文件,并根據Avalon 總線傳輸規范設置好相關的信號線,如圖4所示。這里要注意,使用的是從端口。完成后,將IP核添加至SOPC中,建立內嵌系統,并編譯下載到FPGA 器件中。

評論