混合同余法產生隨機噪聲的FPGA實現

摘要:隨著電子對抗技術的快速發展,在有源式干擾機中需要用到數字高斯白噪聲。通過對混合同余法產生隨機序列的原理研究,本文提出了一種利用FPGA產生高斯白噪聲的方法。該方法在PC主控端的控制下,采用ROM查找表的方式實現信號的產生。在混合同余法的原理基礎上,設計利用 MATLAB和QuartusⅡ軟件對設計的高斯白噪聲發生器進行仿真驗證。應用Verilog HDL語言實現模塊功能性,本設計采用Altera公司的StratixⅣ芯片EP4SGX230KF40C4ES。實驗結果顯示,本設計得到了穩定輸出的數字高斯白噪聲信號。

本文引用地址:http://www.j9360.com/article/201609/303580.htm關鍵詞:高斯白噪聲;混合同余法;FPGA;Verilog HDL

電子戰是戰場敵對雙方保護電磁譜為己所用同時防止被敵所用的科學藝術。電子戰包括電子支持措施(ESM)、電子對抗措施(ECM)、電子反對抗措施 (ECCM)。電子干擾是電子對抗的重要組成部分之一,而有源壓制式干擾是電子干擾中的一種常用手段。有源壓制式干擾一般采用噪聲調制,目的是盡可能大地降低被干擾雷達接收機中的信噪比,從而降低雷達的發現概率。在壓制式噪聲干擾中,噪聲干擾都是采用隨機噪聲信號對VCO進行調制的干擾。因此在電子對抗領域里,噪聲始終是最基本、最常用的干擾源之一。如何產生穩定和精確的噪聲信號已經成為一個重要的研究領域。

隨著FPGA技術的高速發展,數字噪聲發生器的性能也得到了快速的發展。相對于傳統的物理噪聲發生器,基于FPGA的硬件電路噪聲發生器具有實現簡單方便靈活,易于擴展的優勢。文獻提出了一種基于M序列的高斯白噪聲產生方法,該設計選取3個線性反饋移位寄存電路(LFSR),每個時鐘生成一個32bit的均勻分布的隨機數,序列具有的周期大約為288,足以滿足實際工程需要。但是在該設計中1片FPGA內集成了均勻分布白噪聲模塊,FIR數字低通濾波器,均值和方差控制電路,耗費FPGA資源較多,結構較為復雜。

文獻介紹了混合同余法和中心極限定理,論證了在此方法上可以產生服從正態分布統計特性的隨機數。本文在此基礎上,提出了一種基于混合同余法的FPGA隨機噪聲發生電路設計。設計通過主控端控制FPGA從直接波形ROM中讀取數據,節省了FPGA片內的加法器和乘法器資源,結構簡單,可靠性高。

1 混合同余法原理介紹

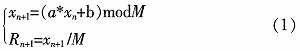

通過同余運算生成偽隨機數的方法稱為同余法,常用的同余法包括加同余法、乘同余法、混合同余法、除同余法。其中乘同余法和混合同余法的性能更好,有速度快、內存省、周期長、統計特性好等優點。混合同余法是Lehmer在1951年提出的,混合同余法是加同余法和乘同余法的混合形式,其迭代式如下:

式(1)中a為乘子,xo為種子,b為常數,M為模。混合同余法是一種遞歸算法,即先提供一個種子x0,逐次遞歸即得到一個不超過模M的整數數列。集合 {xn}是由0到M-1的全部整數重新排列而成。當b=0時,稱此算法為乘同余法;若b≠0,則稱算法為混合同余法。xn是在(0,M)內服從均勻分布的隨機變量,Rn則是在(0,1)內服從均勻分布的隨機變量。式中x0,a,b,M的取值并不是隨意的,模M大小是發生器周期長短的主要標志,常見的M為素數,取b為M的原根,則周期T=M-1。試驗統計表明,用以下參數進行混合同余法產生的隨機序列的統計特性較好:

混合同余法產生的隨機序列具有以下特點:

1)xn重復周期較小,由于xn取值在(0,M)內,其周期,T≤M,T受x0,a,b,M值的影響。另外,在編程時,浮點運算也會對T產生影響。

2)用此方法產生的隨機序列,在一個周期內任意兩個隨機數不可能相等,這往往與實際情況不相符。

經Hull和Dobell證明,只有x0,a,b,M滿足以下一些關系才能實現周期最大化,即T=M,條件如下:

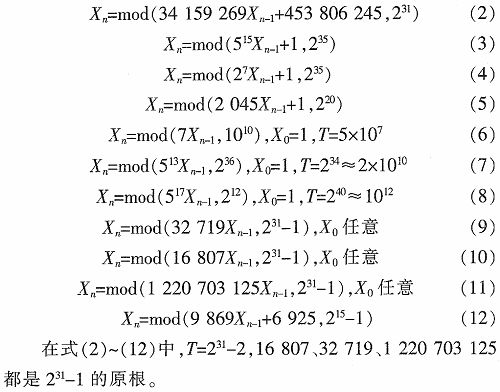

1)b與M互質(或互素,即它們的最大公約數為1)2)設q為某一質數,M分別能被q和4整除,且a-1能被q和4整除產生具有最大周期的偽隨機序列的混合同余法算法為:

由于M=2k,k≥2時,M只有一個素數因子2,且4也是M的因子,此時a=4n+1,正好滿足了T=M的第二個條件;而此時b=2m+1,剛好與M互質,即滿足T=M的第一個條件。

可以看出,混合同余法產生的隨機序列最多只能有M個不同的取值。為了獲得長周期的隨機數序列,應盡可能取大的M值,并合理選擇其它參數。

利用混合同余法產生的是在(a,b)區間上均勻分布的隨機序列,再根據中心極限定理,就可以得到服從正態分布的隨機序列。由獨立同分布中心極限定理有:設隨機變量X1,X2…Xn相互獨立,服從同一分布,且具有數學期望和方差:

2 方案設計

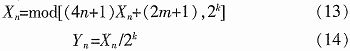

本文設計的高斯白噪聲發生器的系統結構框圖如圖1所示,首先在PC控制端根據式(17),應用MATLAB產生需要的高斯白噪聲數據并存入ROM表,計數器模塊在FPGA的控制下從ROM表中讀出數據送往DAC,通過數模轉換就可以得到高斯白噪聲。

下面對噪聲發生器設計的各個部分進行分析,并在FPGA中仿真實現。

3 系統仿真

在PC主控端,利用MATLAB工具基于混合同余法產生高斯白噪聲數據。圖2是MATLAB仿真結果圖,分別繪出了利用混合同余法時產生的均勻分布序列和在均勻序列基礎上產生的正態分布序列,以及它們的頻率分布情況。從仿真結果可以看出,仿真生成的隨機序列的統計特性和單位正態分布十分吻合。產生的高斯白噪聲滿足噪聲隨機性和統計特性的要求,在PC主控端可以通過改變均值,方差和種子值,從而得到不同的服從正態分布統計特性樣本,從而產生滿足各種需要的高斯白噪聲。將MATLAB仿真生成的隨機信號數據保存成mif文件,存入ROM表中供FPGA讀取使用。

評論