組合邏輯電路的特點及結構分析

組合邏輯電路特點

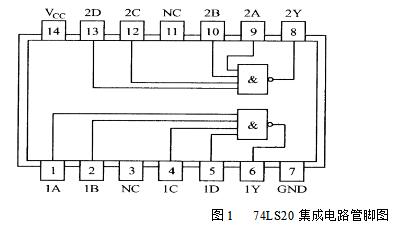

本文引用地址:http://www.j9360.com/article/201608/294840.htm①組合電路是由邏輯門(表示的數字器件)和電子元件組成的電路,電路中沒有反饋,沒有記憶元件;

②組合電路任一時刻的輸出狀態僅取決于該時刻各輸入的狀態組合,而與時間變量無關。

組合邏輯電路結構

組合邏輯電路: 任一時刻的輸出狀態僅取決于該時刻各輸入狀態組合的數字電路。

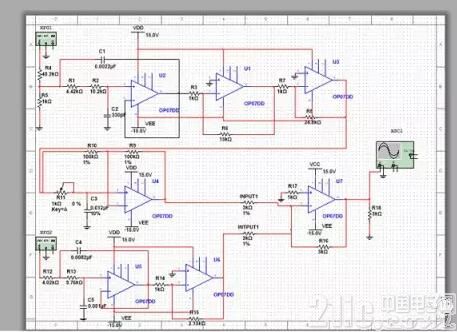

由真值表知,電路將輸入二進制碼A3A2A1 轉換輸出循環碼Y3 Y2 Y1。即任何時刻,輸入一組二進制碼,輸出便是該組碼對應的循環碼,而與時間變量無關。

組合邏輯電路的分析

組合邏輯電路的分析:從給定的邏輯電路圖求出輸出函數的邏輯功能。即求出邏輯表達式和真值表。

步驟一般為:

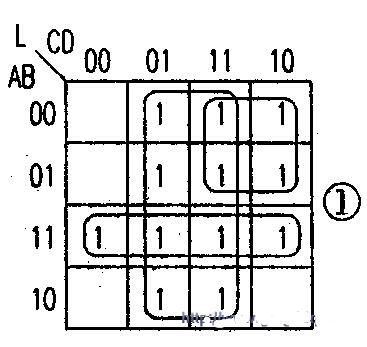

(1)推導邏輯電路輸出函數的邏輯表達式并化簡。

首先將邏輯圖中各個門的輸出都標上字母,然后從輸入級開始,逐級推導出各個門的輸出函數。

(2)由邏輯表達式建立真值表

作真值表的方法是首先將輸入信號的所有組合列表,然后將各組合代入輸出函數得到輸出信號值。

(3)分析真值表,判斷邏輯電路的功能

例 試分析圖所示的邏輯電路圖的功能。

圖 例的電路圖

解:(1)根據邏輯圖寫出邏輯函數式并化簡

(2)列真值表如表。

(3)分析邏輯功能

由真值表可知:

A、B相同時Y=1,A、B,不相同時 Y=0,所以該電路是同或邏輯電路。

評論