基于FPGA的TS流的UDP封裝實現

摘要:為實現數字廣播接收機輸出的傳輸(TS)流方便地接入嵌入式平臺,實現綜合業務接收,本文基于現場可編程門陣列(FPGA),實現了將集成DVB-T(Digital Video Broadcasting-Terrestrial)高頻頭輸出的TS流轉化為UDP協議的IP流,進一步通過以太網接口進入嵌入式平臺,支持綜合業務接收。該接口轉化模塊借助FPGA,將緩存的TS流進行有效封裝,設置以太網接口,輸出UDP格式的IP流。實測表明,該接口轉換模塊可實現TS流到IP流的轉換,支持嵌入式平臺視頻播放與綜合業務接收。

本文引用地址:http://www.j9360.com/article/201607/294698.htm引言

在互聯網高速發展以及三網融合的趨勢逐步推進的背景下,地面數字電視廣播與互聯網的融合得到了研究人員越來越多的重視。地面數字電視廣播[1]音視頻數據的傳輸流是編碼格式為MPEG-2(Moving Picture Experts Group-2)的TS(Transport Stream)流。因此,傳統廣播接收機多輸出TS流。

為支持嵌入式平臺實現TS流傳輸的綜合業務接收,本文在前期實現的數字廣播接收機的基礎上[2],采用FPGA作為轉接,實現了TS流到IP流的封裝,從而可以方便地將TS流接入嵌入式平臺,實現利用嵌入式平臺的基于TS流的綜合業務接收。

1 硬件系統結構

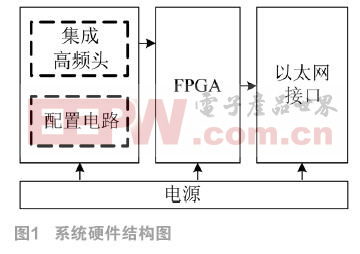

硬件系統主要包括電源部分、集成高頻頭[3]及其配置電路部分、FPGA部分和以太網接口輸出部分。其工作原理如下:系統啟動之后,由配置電路中單片機首先對集成高頻頭進行配置,然后FPGA等待接收由集成高頻頭輸出的數據,接收的數據經過格式封裝后,經以太網接口模塊以UDP格式[4]的IP流輸出。輸出的負載數據為MPEG-2標準的TS包,可以在任何支持該標準解碼的終端進行實時播放。

系統的硬件結構如圖1所示,系統實現的是以FPGA為控制核心的接收、處理和轉發系統,下面介紹每個部分的具體實現。

(1)電源部分

電源部分采用TI公司的LP3906電源管理芯片,該電源芯片被廣泛應用于低功耗FPGA、嵌入式微處理器、DSP等系統的電源管理。其性能優秀,最高輸出效率為96%,最大輸出電流為1.5A。該芯片的輸入電壓為5V直流,由外部電源適配器提供。

(2)集成高頻頭及其配置電路部分

本部分電路由集成高頻頭以及其配置電路組成。集成高頻頭采用夏普公司的VA4M1EE6159。該器件功能是將天線接收到的DVB-T標準信號變頻為中頻信號[5],通過解調、基帶處理和打包,最終輸出TS(Transport Stream)流[6]。TS流輸出有兩種常用接口,分別是異步串行接口(ASI,Asynchronous Serial Interface)和同步并行接口(SPI,Synchronous Parallel Interface),VA4M1EE6159采用同步并行接口,該接口共有11位信號線,包括3位控制信號線和8位數據信號線。3位控制信號分別為時鐘信號MCL、同步信號SYN和數據有效信號VALID。其中,集成高頻頭的時鐘信號MCL輸出為9MHz。SPI接口使用同步控制信號,所以傳輸速率由實際情況決定。

配置電路采用Silicon Lab公司的C8051F120單片機作為集成高頻頭的配置電路控制器。該款單片機兼容8051單片機的指令集,速度是普通8051單片機的數十倍,外部無源晶振為25MHz,最高速度可達100MIPS(百萬指令集每秒),支持JTAG(Joint Test Action Group)調試接口。該單片機具有較高處理速度,對于實現嚴格時序有很大的優勢。

(3)FPGA部分

FPGA部分由FPGA電路及其配置電路組成。FPGA采用的是Xilinx公司的Spartan-3系列XC3S700A芯片。該芯片最大用戶I/O數量為372,具有分布式RAM為92kb、塊RAM為360kb,擁有8個數字時鐘管理單元(DCM,Digital Clock Manager),slice數量為5888。配置模式為JTAG模式和主串(Active Serial)模式。采用的存儲芯片是XCF04S,存儲空間為4M,外部為50MHz無源晶振。

FPGA是系統的控制和計算核心[7],負責接收集成高頻頭的TS流數據,將接收的數據緩存、計算、打包,并驅動DM9000AEP芯片,將處理完成的數據以IP數據報的形式輸出。FPGA芯片使用11個通用I/O與集成高頻頭相連,模擬SPI接口時序接收數據。作為DM9000AEP的驅動源,FPGA的物理管腳與DM9000AEP連接,用于按其控制時序驅動芯片工作。

(4)以太網輸出部分

以太網輸出部分使用的是10M/100M自適應的MAC層接口芯片DM9000AEP。該芯片是支持物理層自協商,支持IEEE802.3u全雙工流量控制的快速以太網接口控制器。輸出物理接口與RJ45相連。該以太網控制器使用的是25MHz的無源晶振,外部電路簡潔。

DM9000AEP擁有4K雙字大小的SRAM塊,可以作為以太網幀結構的緩存。由于以太網幀結構最大為1500字節,所以可以緩存多個相同的幀結構。DM9000AEP有兩個方面的功能。首先是完成與后級網絡設備的物理層協商,建立鏈路;其次是接收FPGA的指令,執行指令、發送已經存在于緩存中的以太網幀以及完成相關鏈路層功能。

系統硬件電路由LP3906模塊提供統一的電源管理。集成高頻頭在配置電路完成配置之后,與天線相連,從天線接收DVB-T信號并將信號解調處理,以SPI接口輸出TS流,是整個系統的數據源。FPGA是系統中樞,它模擬SPI時序接收TS流數據并打包為UDP格式,控制DM9000AEP以IP流輸出。DM9000AEP完成與接收者的物理鏈路建立及輔助的鏈路層功能。

2 基于FPGA的封裝轉發實現

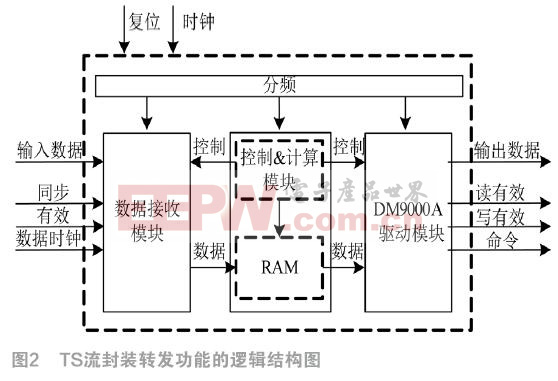

在系統實現過程中,TS流的接收、處理和轉發部分都在FPGA內部實現。圖2為FPGA實現的封裝轉發功能的邏輯結構圖。主體由數據接收模塊、控制計算模塊和DM9000AEP驅動模塊三個模塊組成。數據接收模塊模擬SPI接口時序接收集成高頻頭的輸出數據;控制計算模塊負責將接收的數據有序地存入RAM,并將RAM中的數據打包為IP格式;DM9000AEP驅動模塊將IP格式的數據通過網口輸出。

2.1 數據接收模塊

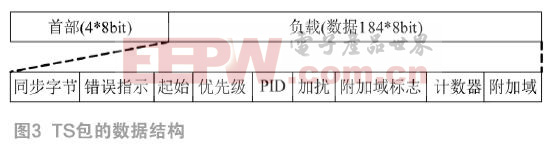

數據接收模塊的功能是模擬SPI接口時序接收由集成高頻頭輸出的TS流格式的數據。集成高頻頭數據輸出寬度為8bit,接口時鐘頻率為9MHz。當有數據輸出時,有效信號變為高電平。輸出的TS流數據包含有4字節的首部和184字節的數據,總計大小為188字節,數據格式如圖3所示。

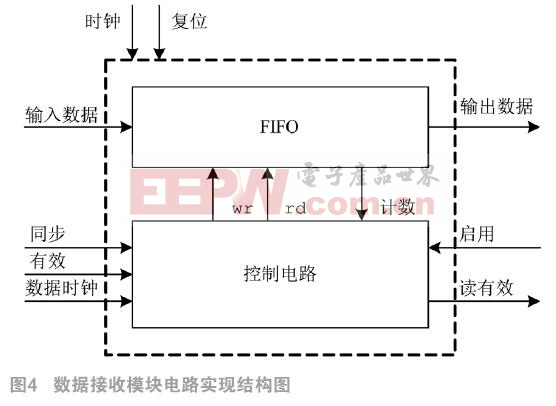

TS流數據輸出為突發模式,即在一個周期內只有小部分時間有數據輸出,大部分時間沒有數據輸出。突發瞬時速率最高可達到72Mbps,這里的72Mbps為裸數據,增加數據頭部等,最高瞬時速率將會增加到80~85Mbps之間。DM9000AEP的理論最高速率為100Mbps。由于在DM9000AEP的驅動中有額外開銷,數據很難做到最大帶寬。所以使用FIFO作為緩沖來匹配前后兩者的速率差,既可以防止數據丟失,也方便進行數據處理。當FIFO中的TS流數據包的數量超過閾值時,則讀有效信號為高電平,數據線輸出數據。本部分電路實現的結構圖如圖4所示。

2.2 控制計算模塊

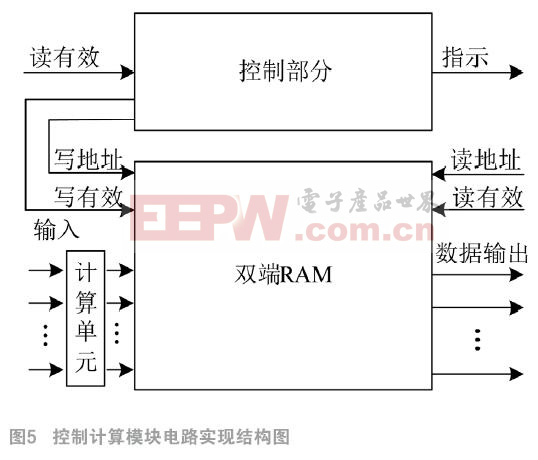

控制計算模塊由控制部分、計算部分和雙端RAM部分組成。本部分電路實現的結構圖如圖5所示。

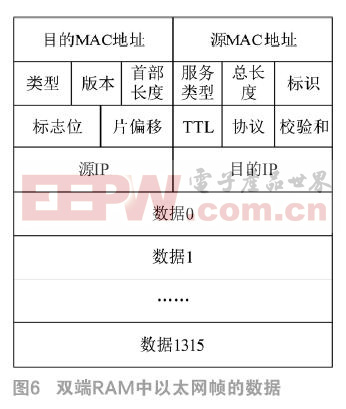

其中,雙端RAM內存儲一個完整的以太網幀,RAM中不同部分的功能如圖6。源MAC地址設置為本機地址,目的MAC地址為廣播地址,類型為IP數據報。IP數據報中版本、首部長度、服務類型、標志位、片偏移、TTL、協議、源IP以及目的IP為常量。其中,源IP設置為本機IP,目的IP為廣播地址,TTL為64。以太網幀的數據大小范圍是46~1500字節。為了最大限度地提高傳輸效率,取7個TS包作為一個以太網幀的數據部分,即1316字節。

以太網幀中數據段、標識字段和校驗字段為變量。數據段由傳輸的TS流數據決定;標識字段為依次遞增;校驗字段則是將字段本身置為零之后,對IP數據報中每16比特進行二進制反碼求和,將結果存入校驗字段。這部分運算在計算部分實現。

控制部分時刻監視讀有效信號的狀態變化。當發現信號狀態變化為有效,則接收前級模塊的輸出數據,并且按地址存入RAM。與此同時,在數據輸入路徑上的計算模塊對數據進行反碼求和運算,得到校驗字段,并且進行遞增運算,得到標識字段。計算完成后,兩個字段分別按地址存入RAM中。此時,RAM中是一個完整的以太網幀結構。控制部分將會給出指示信號,通知DM9000AEP驅動模塊可以讀取UDP幀數據。

2.3 DM9000AEP驅動模塊

DM9000AEP驅動模塊通過狀態機實現,負責對DM9000AEP芯片進行初始化及功能驅動。

DM9000AEP的初始化過程首先進行物理層(PHY)上電。物理層上電第一步是對DM9000AEP芯片內部的GPR寄存器清零,然后最低位賦值為1。在對物理層上電之后,延時應該超過2ms,最佳為5ms。第二步是將NCR寄存器進行兩次軟件復位,兩次軟件復位的目的是確保軟件復位成功。每次軟件復位延時30μs,正常的時間間隔是20μs左右。然后依次按著時序對NSR、ISR、TCR、BPTR、FCTR、SMCR的寄存器和物理地址進行設置。為了確保數據的通用性,物理地址設為廣播地址。寄存器設置成功表示DM9000AEP初始化完成。

初始化完成后的DM9000AEP在檢測到控制計算模塊的指示信號變化后,在雙端RAM的右端進行讀取,將RAM中的一個以太網幀數據寫入DM9000AEP的buffer中,并查詢標志位,直到標志位變化表示發送完成。由于DM9000AEP的發送速度大于集成高頻頭的數據平均輸出速率,所以不會出現雙端RAM中數據被重復寫的情況。

FPGA部分的三個模塊采用的是流式的處理過程。數據接收模塊模擬接口時序接收集成高頻頭的輸出數據,是整個FPGA邏輯的數據源。控制計算部分負責對IP數據報進行計算打包,并且將完整的以太網幀存入雙端RAM,完成之后通知驅動部分。DM9000AEP的驅動部分負責按時序初始化DM9000AEP,并在得到控制計算模塊的通知后,發送雙端RAM中的以太網幀。

3 系統測試

為驗證系統接收數據的正確性及系統運行的實際效果,對系統進行實測。

發送端采用PC機控制調制卡DTA-115產生符合DVB-T標準[8-9]的調制信號。其中,DTA-115為DekTec公司生產的多制式數字電視調制卡。發射端采用QPSK調制,中心頻率為226.5MHz,帶寬為7MHz,2K模式,7/8碼率,發射功率-3dBm。

數字廣播接收系統的數據輸出連接至具有MPEG-2解碼播放功能的嵌入式平臺。單片機設置高頻頭的對應接收參數,FPGA實現數據處理轉發,嵌入式平臺實現TS流的解碼播放。最后嵌入式平臺上測試結果如圖7所示。視頻流數據可以進行流暢播放。

4 結論

本文利用FPGA實現了集成高頻頭輸出的TS流轉換為嵌入式平臺可以讀取的IP流。系統通過集成高頻頭接收DVB-T標準[10]廣播信號,由高頻頭完成廣播信號的接收,得到TS流數據。利用FPGA實現了高頻頭輸出的突發數據的平滑封裝至基于UDP協議的IP數據流。經過測試[11],基于FPGA的封裝模塊輸出的IP流可以在嵌入式平臺播放。

參考文獻:

[1]楊知行,王軍,王昭誠,等.數字電視傳輸技術[M].北京:電子工業出版社. 2011.

[2]戴軍忠,陳為剛,趙玉冰,等. DTMB數字電視接收機電路設計與實現[J].中國科技論文在線,2014-12-12.

[3]Nguyen TT, Dang KL, Nguyen HV, Nguyen PH. A Real-Time FPGA Implementation of Spectrum Sensing Applying for DVB-T Primary Signal [J]. Proceedings International Conference on Advanced Technologies for Communications, 2013:164-169.

[4]史蒂文斯(W.Richard Stevens).TCP/IP詳解卷1:協議 [M].北京:機械工業出版社.2000.4.

[5]Gholami M, Rahimpour H, Ardeshir G, Miar-Naimi H. A new fast-lock, low-jitter, and all-digital frequency synthesizer for DVB-T receivers [J]. International Journal of Circuit Theory and Applications, 2015, 43: 566-578.

[6]丁法珂,基于FPGA的PCM-FM遙測中頻接收機設計與實現[J].電子產品世界,2015,6:54-59.

[7]張黎明, 高性能數字接收機FPGA設計[J].電子產品世界,2013,5:40-42.

[8]Torio P, Sanchez MG. Reconciling the ETSI coverage requirements for DVB-T with the ITU-R recommendations[J].Telecommunication Systems, 2014,57:217-222.

[9]DVB Document A122. Digital Video Broadcasting (DVB). Frame structure channel coding and modulation for a second generation digital terrestrial television broadcasting system. v1.3.1 [S]. 2011.

[10]ETSI EN 300 744 V1.6.1 Digital Video Broadcasting (DVB). Framing structure, channel coding and modulation for digital terrestrial television [S]. 2009.

[11]陳為剛,趙干,李思,等. 基于USRP的DVB-T接收機實現 [J]. 電視技術,2014,38(9):155-159.

本文來源于中國科技期刊《電子產品世界》2016年第7期第51頁,歡迎您寫論文時引用,并注明出處。

評論