下一代基帶芯片大戰開打

全球主要的電信晶片供應商高通(Qualcomm)、DSP核心供應商CEVA以及處理器核心業者ARM,均競相迎接這一挑戰。三家公司均已開發出新的處理 器架構,并搶先在今年的世界行動通訊大會(MWC)之前發布。高通宣布Snapdragon X16、CEVA發表CEVA-X4,ARM則暢談其新款Cortex-R8。

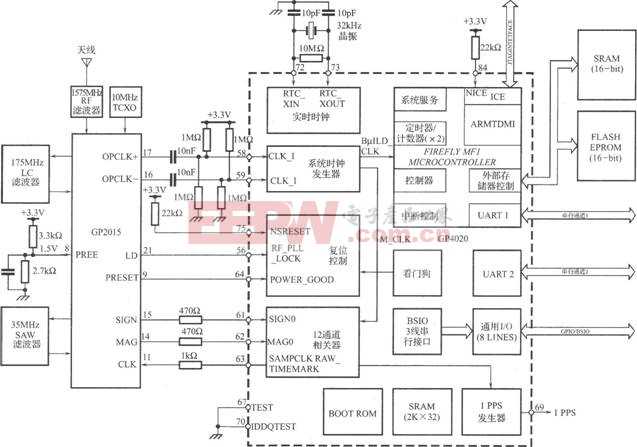

高通新款數據機晶片在其Hexagon DSP核心中執行密集的LTE協定和語音編解碼器(codec),同時還采用ARM Cortex執行Linux作業系統(OS)、IMS和IP堆疊。

挑戰何在?

那么,這些新的基頻數據機有何不同之處?

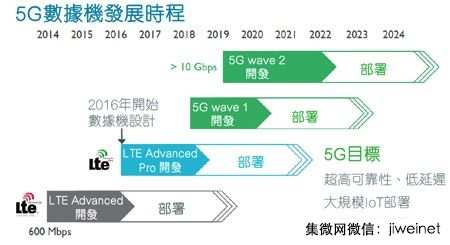

與 該技術有關的議題包括:增加載波聚合(CA)、將多重無線存取技術(Multi-RAT)整并于單一數據機、切換不同數據機時的低延遲作業、同步處理雙基 地臺以及伴隨VoLTE高品質語音通話服務而來的復雜度等。根據CEVA,新的基頻據機必須能夠處理上述所有或更多的問題。

The Linley Group資深分析師Mike Demler呼吁為現有的數據機晶片架構進行“全面體檢”,“才能滿足LTE Advanced(LTE-A)與LTE-A Pro標準日益嚴格的性能和功耗限制。”

因此,存在于高通、CEVA和ARM三方之間的競賽,開始轉變成為針對處理器、硬體加速與DSP的全新戰場。

供應商們正積極討論在Layer 1實體(PHY)控制器、Layer 2和layer 3處理之間增加的LTE基頻工作負載應該如何進行最佳化處理;以及應該采用先進的DSP核心、強化的處理器核心或是二者兼用的組合?

各據不同勢力范圍的每一家供應商顯然有著不同的想法。

高通發表先進的LTE數據機Snapdragon X16,用于支援LTE-A Pro Category 16高達1 Gbps傳輸速率的下行鏈路以及實現Category 13高達150Mbps的上傳速度。

高通最新Snapdragon X16支援高達1 Gbps的下載速度,號稱是行動產業首款Gigabit級的LTE數據機

為了不讓高通專美于前,CEVA和ARM也發布自家最新設計的核心——分別是CEVA-X4與ARM Cortex-R8,他們表示最新的架構已經準備好迎接LTE-A Pro數據機的挑戰了。不過,目前還沒有任何一款商用基頻晶片采用任一家IP供應商的處理器核心。

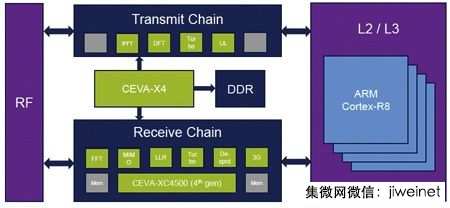

因 應LTE-A Pro數據機晶片日益增加的處理需求,兩家IP核心供應商顯然采取了全然不同的發展重點。例如,CEVA以CEVA-X4更新其L1 PHY控制器。相反地,ARM則透過其最新設計的四核心Cortex-R8,專注于滿足針對Layer 2與L3軟體處理持續增加的需求。

Demler明確指出,Cortex-R8和CEVA-X4是兩種完全不同的核心。CEVA-X4用于PHY層控制,而ARM Cortex-R則否。他強調,“X4和R8可能在一款數據機應用中共存,讓X4處理實體層,而Cortex-R則處理更高層級的控制功能。”

CEVA-X4與ARM Cortex-R8可能共存于下一代數據機晶片中?

遭遇瓶頸

CEVA行銷與企業發展副總裁Eran Briman指出,在詳細研究最新先進基頻數據機的需求后,“我們發現PHY控制器在下一代基頻中的瓶頸。”

藉由為基頻應用重新定義處理控制和資料平面的性能和能效,CEVA開發出全新的CEVA-X DSP架構。

CEVA-X4是來自CEVA-X架構的首款授權核心。雖然DSP一直是CEVA的強項,但Demler 認為,CEVA-X4更像是“一款具有DSP功能的控制器。”

CEVA無線業務部業務開發總監Emmanuel Gresset解釋,在CEVA-X4中增加的CEVA先進DSP功能結合了控制層處理,以及“協同處理器和硬體加速的支援。”

他認為CEVA-X4是一種“全新的處理器類型,它能在DSP與控制之間實現真正的平衡。”

Gresset 還指出,CEVA-X4的CoreMark/MHz基準達到了4.0。CoreMark是專為嵌入式系統衡量CPU性能的基準。Gresset說,這對于 CEVA來說是非常重要的,因為CEVA-X4目前可說是“與ARM Cortex-R7/R8不相上下。”

新的CEVA-X4架構充份結合控制器與DSP處理器,瞄準手機、IoT裝置以及下一代5G基頻數據機等應用

捍衛L2/L3處理領域

ARM一直是智慧型手機市場中首屈一指的CPU核心供應商。

ARM先進技術行銷總監Chris Turner解釋,“ARM Cortex-R7目前部署于大量3G/4G智慧型手機數據機中,Cortex-R4和Cortex-R5也用于ARM合作夥伴的數據機產品中。”

藉著Cortex-R8的推出,ARM計劃滿足對于協議軟體處理以及LTE-A Pro與第一代5G日益增加的需求。他并補充說,“我們期望看到新的基頻設計提升到采用Cortex-R8。”

值得注意的是,Cortex-R是為硬即時應用而最佳化的,Turner因此稱Cortex-R8是“專為5G性能打造的唯一即時處理器。”

不過,奇怪的是,高通顯然并未在其新款Snapdragon X16數據機中采用ARM核心,反而改為部署自家的DSP來處理LTE-A Pro的工作負載。

ARM Cortex-R8和R7的最主要區別在于R8支援多達4顆超純量亂序執行的核心。此外,ARM表示,R8還配備“高達每核心2MB緊密耦合記憶體”的更大容量。

隨著5G的資料傳輸速率大幅提升,Cortex-R8兼具低延遲、高效能與低功耗的優勢,有助于打造支援LTE-A Pro和5G的數據機

針對數據機晶片的其他部份,Turner坦承“實體層是十分復雜的工程,包括類比轉換、DSP進行調變與解調、Turbo編碼、錯誤檢查與加速加密,以及標頭壓縮等。”

那么ARM Cortex-R系列核心如何與其連接?Turner說,“的確,有些技術可以從專業的IP供應商授權取得,但他們通常還得進行修改或配置,才能用于一家公司專有的數據機架構。”

他補充說,“我們在這些設計中看到ARM Cortex-R系列處理器出現在軟體接觸實體層(Layer-1)硬體之處,并根據不同的標準,為管理與排程連接的所有軟體提供Layer-2與Layer-3處理。”

此外,他表示,ARM的處理器還可執行Layer-1控制軟體,配置與管理連接至Layer-1硬體(包括DSP與本地化控制邏輯)的介面。

是否重疊?

然而,CEVA看這一競爭格局的觀點略有不同。Gresset指出,ARM的Cortex-R7或R8在這方面的應用,“缺少了DSP和系統控制。”他解釋說,這使得ARM難以擴展Cortex-R在處理PHY控制器的角色。

Gresset還補充說,“相較于CEVA-X4采用VLIW/SIMD核心,ARM的R7/R8由于采用超純量亂序架構,使得晶片尺寸較大,每核心也消耗更多功耗。”。

因 此,Gresset 強調,CEVA雖然藉由增加更多硬體加速來捍衛其于Layer 1 PHY控制器的地盤,同時也希望創造一個可提升至Layer-2與Layer-3處理的開始,盡管這一向是ARM占主導的領域。他將強大的DSP處理(高 達16GOP)、高效的控制器性能以及先進的系統控制稱為“CEVA-X新架構的三大支柱”。

另一方面,ARM則認為,Cortex-R8的關鍵優勢在于其“在4個一致的核心與介面擴展數據機軟體”的能力。其目標在于為密集的即時軟體工作負載“實現平行化,以及滿足LTE-A與LTE-A pro所需的性能與時機”。

評論