摩爾定律邁入“后CMOS”時代

在英特爾(Intel)負責晶圓廠業務的最高長官表示,摩爾定律(Moore’s Law)有很長的壽命,但如果采用純粹的CMOS制程技術就可能不是如此。

本文引用地址:http://www.j9360.com/article/201602/286634.htm“如果我們能專注于降低每電晶體成本,摩爾定律的經濟學是合理的;”英特爾技術與制造事業群(technology and manufacturing group)總經理William Holt,在近日于美國舊金山舉行的年度固態電路會議(ISSCC)上對近3,000名與會者表示:“而超越CMOS,我們將看到所有東西的改變,甚至可 能是電腦的架構。”

Holt婉拒分享他所說的“豐富多樣化”后CMOS (post-CMOS)技術,會有哪些獲得晶片制造商采用、或是何時采用;那些新技術包括自旋穿隧場效電晶體(span tunneling FET)、鐵電FET、自旋電子、新一代三五族材料…等等。但他聲明這些新技術不會出現在英特爾正在制作處理器圓形的10奈米制程。

在一般情況下,工程師們會盡可能延展CMOS技術的壽命;Holt表示,長期來看,晶片制造會是不同技術與傳統CMOS的混合:“我們將看到混合的操作模式…(晶圓的)某些部份采用CMOS技術,相同晶圓上的新元件則為不同的優勢最佳化。”

他 對于將照亮接下來十年半導體產業發展路徑、顯然還需要龐大研究工作的技術提供正面看法:“我不能告訴你在那些(后CMOS)技術中,哪個排第一或是最棒, 但是我們看到其中豐富的可能性…將在接下來幾年提供大量的機會,讓我們在打造零件所需的技術上取得重大進展;而挑戰在于厘清如何實現它們。”

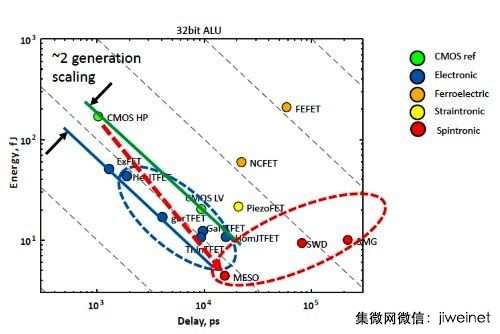

到目前為止還有個大挑戰,是所有的后CMOS替代技術都有助于降低功耗,這是一個首要考量,但它們的執行速度顯然比起CMOS電路緩慢得多;Holt拿這個問題與一個世代以前工程師為了因應當時緊迫的功率需求、從雙極架構轉為新的復雜CMOS的狀況比較。

很多種類的后CMOS技術都能降低功耗,但也導致延遲

Holt表示,產業界需要專注于降低功耗與降低每個電晶體的成本;他重申英特爾已將22奈米與14奈米制程節點電晶體成本降低30%、稍優于業界水準的聲明,不過開發最近幾個新制程節點的成本增加幅度,由傳統的10%增加到了30%。

他指出:“現在預測7奈米節點的細節還太早,但我們可以說,我們在7奈米節點的每電晶體成本降低幅度,在歷史線的范圍內可能會更多──我們看到了一些降低成本的可行途徑。”

在專題演說之后,Holt澄清,對英特爾7奈米節點的預測,目前落到延續自傳統電晶體成本下降趨勢、到英特爾在22奈米與14奈米節點收獲的些微改善之間的范圍內:“不確定因素還很多,所以我們不知道我們會落在哪個點上。”

英特爾一直都沒有放棄希望,認為可能在7奈米制程量產開始后的某個時間點開始采用超紫外光(EUV)微影技術;EUV可能對7奈米制程的成本帶來顯著的影響,降低對多重圖形(multi-patterning)的需求。

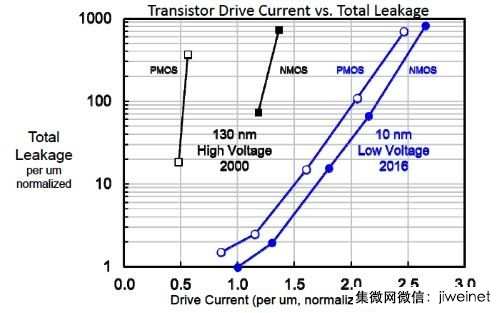

此外Holt還指出英特爾10奈米制程將支援5個等級的電壓閾值,在既定節點內的最佳化點(optimization points)之多樣化,可能會隨著后CMOS技術的加入而提升。

Holt表示,英特爾的10奈米制程將支援五種電壓閾值,提供更多功率選項遲

評論