低功耗8-bit 200MSPS時間交織流水線ADC

摘要:本文介紹了一款低功耗8位200MSPS的模數轉換器。ADC是由時間交織和逐級遞減技術來實現低功耗的。流水級和放大器的設計保證了低電流下滿足工藝、電壓、溫度(PVT)變化。本ADC采用0.35μm 雙層多晶硅柵三層金屬的CMOS工藝,在200MHz采樣頻率和41MHz輸入信號頻率下達到47.7dB的SNDR。在3V的電源電壓下功耗僅為120mW,不包括輸出緩沖器。

本文引用地址:http://www.j9360.com/article/197924.htm引言

移動無線通信系統是模擬數字轉換器的主要應用。高性能的交流特性,主要包括信噪比(SNR)和無雜散動態范圍(SFDR),能夠提供更好的無線通信覆蓋率,更多的載波,更好的質量和可靠性。功耗和面積對于移動無線通信系統也非常重要。

在多種ADC中,流水線ADC是最適合做高速高精度的。目前的設計趨勢是在低功耗下實現高性能。運放共享及開關運放技術被廣泛地應用于降低功耗上[1-3]。但是此技術只適合低速ADC。本文中采取的一些技術可以在不犧牲性能的情況下來節省功耗。該ADC在200MSPS,輸入信號頻率為41MHz時達到47.7dB的信噪比,電流僅為40mA。

論文的組織如下:第二章介紹流水線ADC的結構。第三章介紹了流水級、放大器和基準產生電路等的具體結構。第四章給出最終的測試結果。

流水線ADC的結構

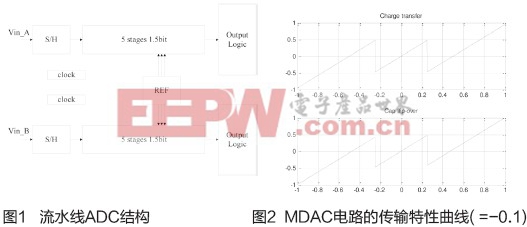

流水線ADC有兩個通道,每個通道都工作在100MHz下,包括5個1.5 bit流水級和一個3bit flash ADC。傳統的轉換器。第一級流水級一般為多位數,例如3.5bit或4.5bit。但在文中采用的是1.5bit的。其中有兩個原因:第一,文中ADC是時間交織的。它有兩個通道,任何不匹配都會降低性能。第一級的多位數會引起比1.5bit更多的失配,因為多位數相對于1.5位會有更多的電容和開關。第二,在8位100MHz ADC中放大器功耗不大,所以第一級選取多位數并不比采用1.5bit和逐級遞減技術的更省功耗。系統結構如圖1所示。

流水線ADC中還有基準源和時鐘等。基準源必須滿足PVT變化,所以要仔細設計符合要求;時鐘發生器為所有流水級提供時鐘,時鐘偏移會嚴重影響性能。時鐘的驅動必須設計適當,如果驅動太大會消耗過多的功耗,而版圖中會有很多寄生電容,所以為保證性能要留一些裕度。

電路實現

流水級

流水級有三種結構:開環,閉環電荷轉移,閉環電容翻轉[4]。開環結構可以降低對放大器的要求,但是由于嚴重的非線性必須要有后臺或者前臺的數字校正電路。在8位100MSPS流水線ADC中,放大器的設計并不是瓶頸,所以并不選擇開環結構。兩種閉環結構在理想情況下有相同的功能,但他們在有電容失配的情況下則表現不同。電荷轉移結構的傳輸函數如下[5](Cs/Cf=1不考慮其它的非理性因素):

Vin是輸入信號, 是電容失調,D是數字輸出,Vref 是基準電壓,電容翻轉結構的傳輸函數如下:

圖2為兩種結構在電容失配10%時的傳輸特性曲線 (Δ=-0.1):

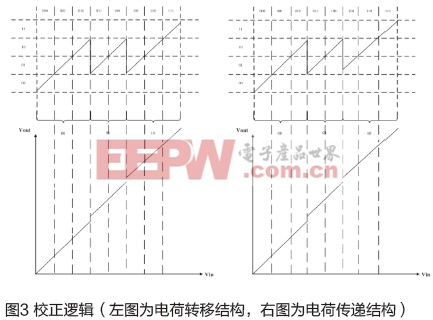

如圖2所示,對于電荷轉移結構來說,第一個和最后一個交叉點總是位于-1/2 和 1/2處,但輸出幅度會被Δ影響。對于電容翻轉式結構,第一個和最后一個交叉點會被Δ影響,但是輸出幅度不會被Δ影響。在電荷轉移結構的-1/4 和1/4處的跳變高度相對電容翻轉式結構來說更接近Vref,分別為0.95Vref和0.9Vref。流水線ADC一般采用冗余位用來校正。如果失調只發生在第一級(假設其他級都是理想的且都是2bit),那么校正過程如圖3所示。

電子管相關文章:電子管原理

adc相關文章:adc是什么

模數轉換器相關文章:模數轉換器工作原理

負離子發生器相關文章:負離子發生器原理 電荷放大器相關文章:電荷放大器原理 離子色譜儀相關文章:離子色譜儀原理

評論