基于PCI Express總線的數據采集設備的實現

1 引言

本文引用地址:http://www.j9360.com/article/195819.htm隨著計算機技術的發展,數據傳輸帶寬的日益增長,總線技術也在迅速的發展。高速信號傳輸,海量數據采集與記錄,實時視頻圖像處理以及其他數據處理的數據吞吐量現以kMb/s為量級。

未來計算機系統對帶寬和擴展性的要求已經超越了第二代總線技術。第三代高性能I/O總線技術――PCI Express(PCIE)總線解決了以往總線的不足,它的發展將取代第二代總線成為新的數據總線,其提供了更加完善的性能、更多的功能、更強的可擴展性和更低的成本。

本文研究PCI Express總線技術的發展與構架,介紹采用Xilinx公司的FPGA與NXP公司的PHY器件實現一種經濟簡單的數據采集設備。在電路設計中,分析了總線信號高速布線的要求。

最后詳細介紹數據采集設備的數據通道部分在Xilinx Pipe Core中的實現,并通過WinDriver軟件開發簡單的驅動程序。

2 PCIE總線發展和構架介紹

2.1 PCIE總線的發展

PCI Express是用來互連諸如計算機和通信平臺應用中外圍設備的第三代I/O總線技術,第一代總線包括ISA,EISA,VESA和微通道(Micro Channel)總線,而第二代總線則包括了PCI,PCI-X和AGP。PCIExpress是一種能夠應用于一點設備、臺式電腦、工作站、服務器、嵌入式計算機和通信平臺等所有周邊I/O設備互連的總線。

PCIE最初由InteI發展,并于1992年在市場發布。PCIE的體系結構繼承了第二代總線體系結構最有用的特點,并且采用計算機體系結構中新的開發成果。它保留了原先的通訊模型和下載配置機制,但拋棄了共享總線的方式,采用點到點的總線連接方式。由于它提供了更高的性能特點和越來越大的帶寬,從而解決了PCI,PCI-X和AGP的許多缺點,是以后PC發展必然采用的接口總線,其必將取代PCI,PCI-X以及圖形加速器(AGP)。

2.2 PCIE總線的構架

PCI Express保持了與PCI尋址模式(加載-存儲體系結構具有單層地址空間)的兼容性,從而保證了對現有應用程序和驅動的兼容性。同時,PCI Express的配置機制是與PCI一致的即插即用標準。

軟件層發出讀寫請求,使用基于數據包、分段傳輸的協議通過物理層傳輸至I/O設備。鏈路層向這些數據包添加序列號和循環冗余校驗(CRC)以建立一個高度可靠的數據傳輸機制。基本的物理層包括傳輸對和接收對兩個單工通道,統稱為一個信道。1個lane的信道可以保證每個方向約250 MB/s標準帶寬,這其中大約200 MB/s用來傳輸數據,其余被文件的協議部分占用。這一速率為一般PCI設備的2~4倍,同時PCIExpress總線點到點的總線連接結構可以讓每個PCIExpress設備都具有這個帶寬。

3 基于FPGA與PHY器件的采集設備實現

3.1 采集通道器件和FPGA的選型及設計

采集設備包含2個采集通道,采用模/數轉換芯片ADS5102設計。ADS5102是德州儀器的一款10 b-65MSPS采樣率并帶內部電壓參考的模/數轉換器,采用1.8 V模擬供電。與同一類型的ADS5103相比,它的采樣率更高,而且采用差分信號輸入,有效地提高了輸入信號的共模抑制比。

FPGA選用Xilinx公司Spartan-3系列XC3S1000。其采用90 nm材料生產,容量高、成本低,具有業界一流的區塊和分布,具有多達784個I/O,MicroBlaze 32位RISC軟處理器和支持乘法累加器(MAC)功能的嵌入XtremeDSP功能。

Xilinx Spartan-3 PCI Express設計包括一個PCIExpress Pipe Endpoint LogiCore。Xilinx低成本Spartan-3系列提供PCI Express協議層核。PCIE PipeEndpoint LogiCORE整合了分立的PCIE PHY,提供了全面的、完全符合PCI Express基礎規范(PCI Express Base Specification)v1.1的PCIE端點解決方案。

3.2 外部PHY器件PX1011A

NXP公司的PX1011A符合PCI Express規范v1.0a和v1.1,是一款與低成本FPGA一起使用而優化的單通道2.5 Gb/s的PCI Express PHY器件。

數據由接收器的差分輸入接口進入PXl011A,在被傳送到解串化電路之前,這些數據將小振幅的差分信號變為軌對軌的數字信號。一個載波檢測電路將檢測線路上是否有數據并將這些信息傳送到串行器/解串器SERDES和物理編碼子層PCS。SERDES將這些數據串并轉化為10位并行數據。然后PCS采用8位/10位解碼器來恢復成8位數據格式。

在發送過程中,來自Pipe接口的8位數據通過一個8位/10位編碼算法進行編碼。8位/10位編碼確保串行數據被直流平衡以避免交流耦合系統中的基帶漂移,它同時確保足夠的數據轉換以避免接收端的時鐘恢復。

PX1011A的MAC接口采用獨立的時鐘,由片內100 MHz的基準時鐘鎖相環產生。鎖相環有一個相對較高的帶寬來實現可選的擴頻并較少EMI。8 b數據接口在250 MFIz上運行并進行SSTL2信號發送,這種模式與流行的FPGA I/O接口兼容。

3.3 硬件電路設計

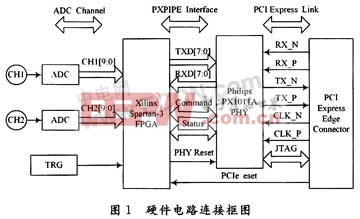

采集部分硬件電路包含2個通道的ADC和觸發電路,每通道ADC轉換后的數據CH1[9:0]和CH2[9:0]傳輸到FPGA端口。PCIE接口電路包括3個部分:第1部分是PX1011A與FPGA的連接信號線,包括8位的收發信號TXD[7:0]和RXD[7:0];控制信號RX_DATAK,RX_VALID,RX_CLK,RX_EIDLE,RX_POLAR,RX_PHY_STAT,TX_DATAK,TX_CLK,TX_EIDLE,TX_COMP,TX_DET_LOOP,TX PWRDN0,TX_PWRDN1,狀態信號STAT0,STAT1,STAT2和復位信號RESET。第2部分是PX1011A與PCIE接口的連接信號線,包括差分接收信號,差分發送信號,差分時鐘。第3部分是PCI Express的配置接口,包括PCIE_TMS,PCIE_TCK,PCIE_TDO,PCIE_TDI和PCIE_TRST。如圖1所示。

評論