寬范圍高穩晶振頻率穩定度測試系統的設計

0 引 言

高穩定度石英晶體諧振器(簡稱高穩晶振)是廣泛應用于通訊、電子對抗、數傳電臺、計算機等電子信息產品的重要器件。高穩晶振的指標直接影響產品的可靠性,因此如何檢測其性能是非常重要的。

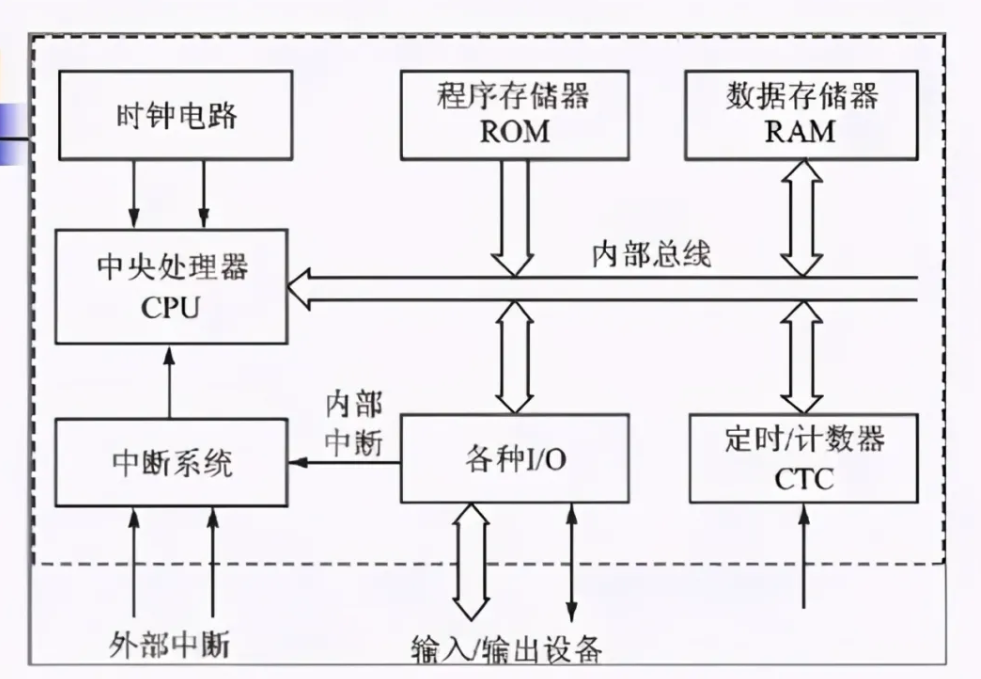

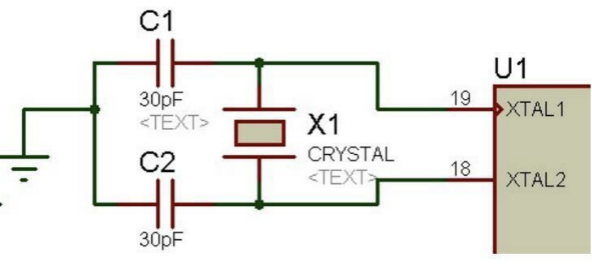

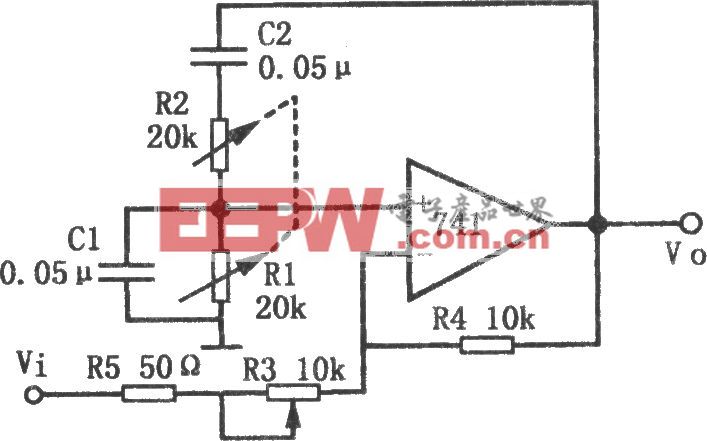

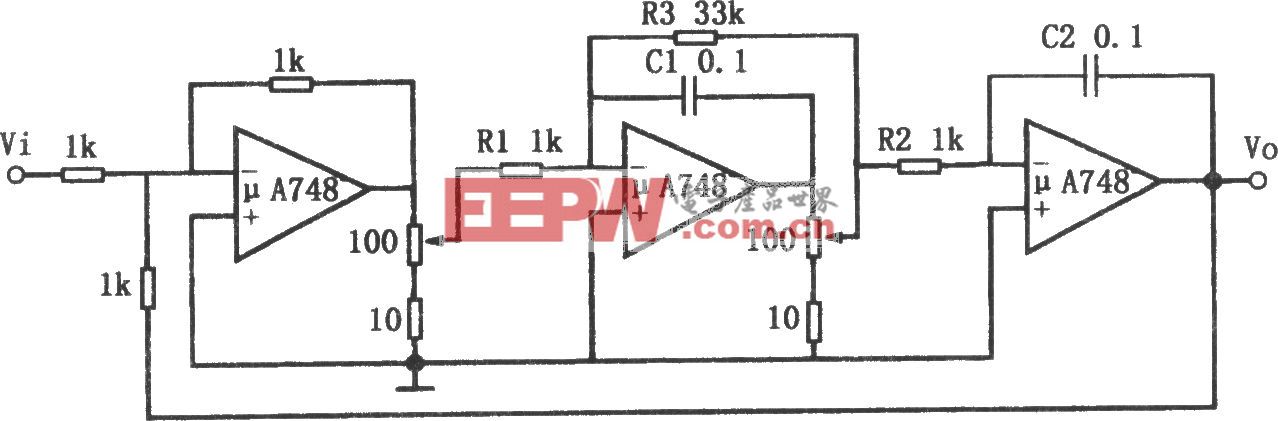

代表性測量儀器是頻穩測試系統(誤差倍增器+多路開關)。其原理是將被測頻率源的頻率起伏△f進行倍頻,然后再用頻率計數器進行測頻來計算準確度、老化率、日波動等指標。在頻穩測試系統的設計中,信號源是一個重要的組成部分。其作用為產生高性能的輸出頻率(1~100 MHz)可設定的鐘信號,與被測晶振的信號進行混頻,輸出差值在倍頻環的范圍內。目前,它廣泛應用于信號源設計的直接數字頻率合成(DDS)技術,具有輸出頻率范圍寬,分辨力高,相位噪聲低,易于實現等優點;其次,對于高分辨力頻率計數器,在同等條件下,頻率分辨高一位,倍增環路可少一路。經比較分析,選擇以DDS技術為核心,采用AVR單片機和CPLD作為控制系統,可適時控制、計算、處理,并與上微機相連,完成多路檢測、分析、繪制狀態圖等工作。

1 頻率誤差倍增法測頻的基本原理

設Fr為標準鐘(銣原子鐘)頻率,被測頻率Fx=Fr+△f。通過第一級倍增得到Fr+m△f,通過第二級倍增得到Fr+m2△f……,通過n級倍增,則有:

![]()

一般m=10,n=1,2,3,4,由于受倍頻器本底噪聲的影響,最高n=5級。頻差倍增最大達10-5。

由式(1)可知,頻穩測試系統只對接近標準鐘輸出頻率的被測信號進行測量。因此,需要研制高性能的新一代測試系統,檢測高穩晶振生產的質量。

評論