一種高精度中頻信號數據采集卡的硬件設計

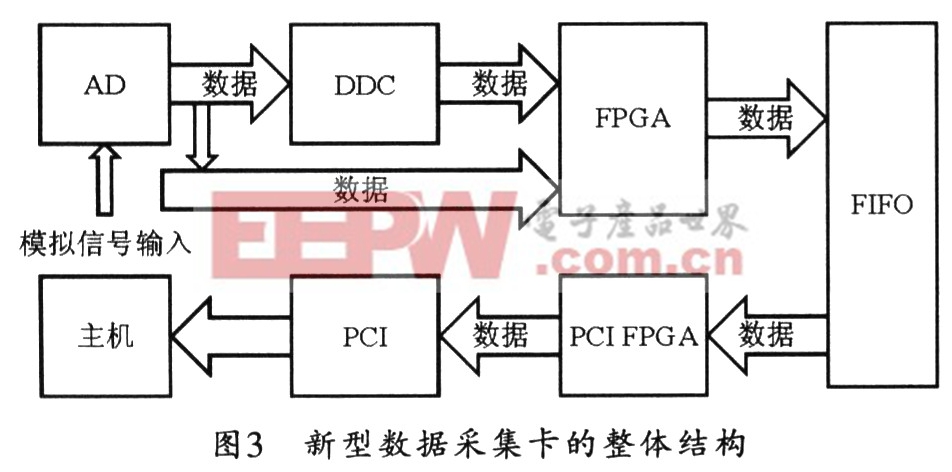

圖3所示為新型數據采集卡的整體結構框圖。由圖3可見,該采集卡結構中主要包括AD采樣、DDC處理、FPGA邏輯控制、緩存以及接口等幾部分。本文引用地址:http://www.j9360.com/article/195595.htm

3.1 AD采樣

本采集卡要求采樣精度為14位、采樣速率最高為100MSPS,為此,可選用美國Analog公司的AD6645。為了保證14位精度,AD6645的時鐘信號應由高穩定性、極低相位噪聲的時鐘源提供,同時,為了達到最佳性能,AD6645的時鐘還應采用差分輸入,因為差分輸入方式能改善對高次諧波的抑制,同時對于電源或地線上的寄生噪聲以及由于反饋引起的本地振蕩等共模信號也有很高的抑制能力。

此外,AD采樣后所得到的數據可分兩路進入FPGA,其中一路直接進入FPGA,待采樣數據進入FPGA后,再做處理;另一路經數字下變頻器,對采樣數據進行下變頻處理后再進入FPGA。

3.2 數字下變頻

數字下變頻的主要作用是將A/D采樣所得到的中頻信號進行下變頻處理后移至基帶。它主要利用數控振蕩器(NCO)產生與輸入中頻信號頻率相同的正弦和余弦本振信號,再經混頻后對結果做低通濾波,即可完成對中頻信號的下變頻操作。

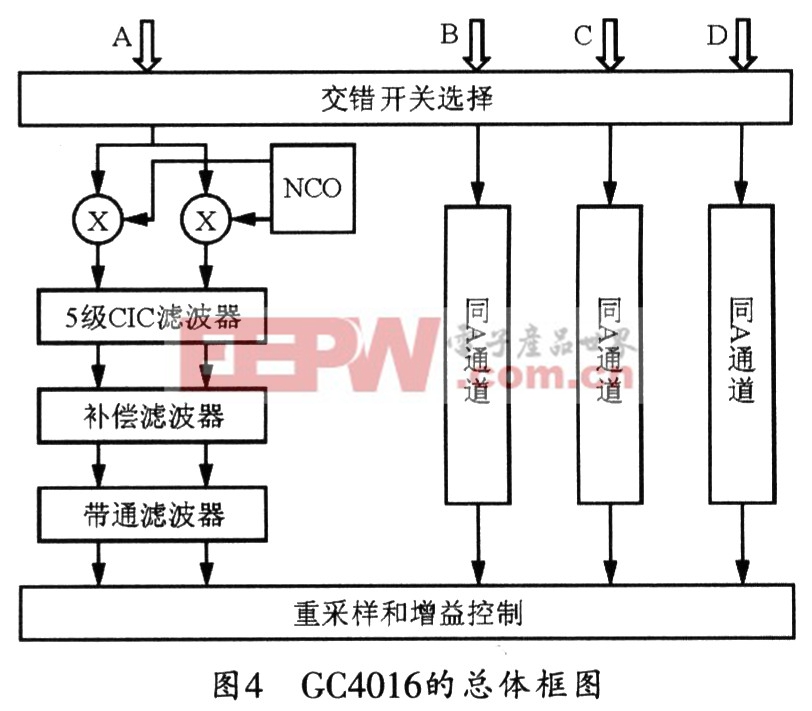

GC4016是Graychip公司推出的專門用于數字下變頻的芯片,該芯片內置4個獨立的相同下變頻電路,它可將一個高達90 MHz的實采樣信號下變頻到任意頻率,其內部的抽取濾波器還可以將輸出速率降到采樣速率的l/32倍到1/16384倍。GC4016的總體框圖如圖4所示。圖4中的交錯開關用于控制輸入數據與下變頻通道的對應關系。

從功能上來看,數字下變頻器主要包括兩個部分,第一部分是數字控制振蕩器(NCO)和混頻器,主要用來把數字化的中頻信號搬移到基帶;第二部分是多級抽取,用以得到期望的載波頻率。

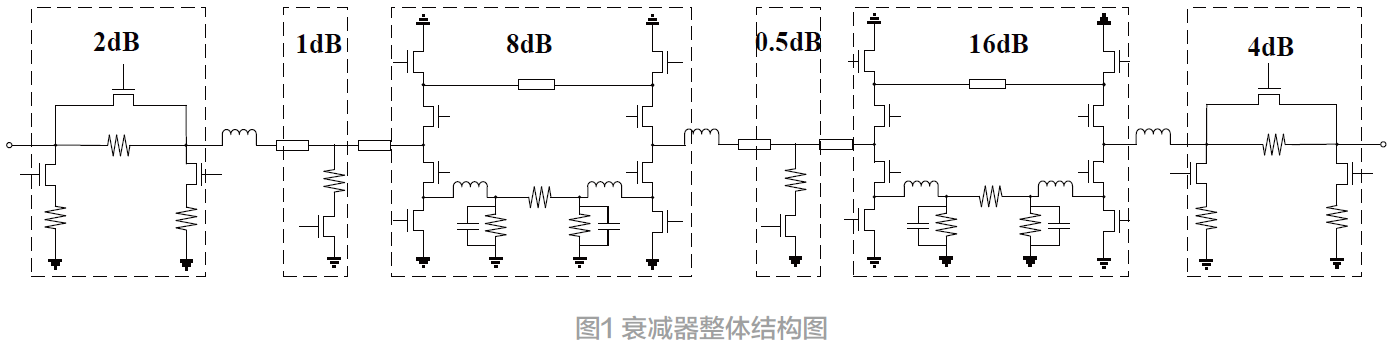

可以看出,DDC抽取部分由3個FIR濾波器級聯構成,其中一個是級聯積分梳狀(CIC)抽取濾波器,另外兩個是抽取因子為2的可編程抽取濾波器。CIC濾波器相對來說結構最簡單,乘法運算比較少,只使用加法和延遲運算,可對信號進行粗略的低通濾波,適合于處理高速率的數字信號,而且抽取因子是可編程的,這是滿足通帶頻率參數和多速率處理的關鍵,可降低后級濾波器的復雜度。當然,由于是粗濾波,它的幅度響應不夠理想,也可能在通帶內對有用信號進行衰減。緊接著CIC濾波器是補償FIR濾波器(CFIR),其結構相對也比較簡單,只有2l階,主要功能是補償由前級CIC濾波器引起的衰落,同時對信號進行進一步的低通濾波和2倍抽取。最后一個級聯的是可編程FIR濾波器(PFIR),結構最復雜,有63階,因此一般放在末級,用來處理低速信號,可對信號進行2倍抽取并完善濾波效果。

總的來說,CFIR和PFIR都是線性相位濾波器,在數據轉換中,都具有很好的特性。

信號經過混頻和濾波后,再就是重采樣,重采樣會獨立地濾波并改變每個通道的輸出數據率。重采樣通常用來增加采樣數據率,以滿足與外部電路所要求的字速率和位速率的匹配。

GC4016可以通過合并通道來增大輸出信號的帶寬,即增大數據速率。即可以將A、C合并為一個通道,B、D合并為一個通道,合并后的輸出數據率是原來的2倍。通常最大可將帶寬增大為原來的4倍。

評論