多路跟蹤濾波同步數據采集系統的研究

介紹了采用高速硬件鎖相環技術,對多路相關聯信號同時、同步整周期均勻采樣和抗混疊跟蹤濾波的實現方法。給出了基于此方法由TMS320LF2407和AD73360L構成的多路數據采集與處理系統。提出一種不同結構的同步串行口接口電路的設計方法,給出了電路連接與軟件流程。

關鍵詞:數據采集 跟蹤濾波 同步采樣 抗混疊

目前同步采樣實現方法主要有兩種,一種是使用多片采樣保持器、多路模擬開關和單片單通道逐次逼近型高速A/D轉換器,再輔以同步信號產生電路,這樣可同時采集多路信號送采樣保持器保持,然后通過模擬開關切換分別送入A/D轉換器進行轉換。該方法使用一片高速A/D轉換器實現多路信號同時采樣。但外置多片采樣保持器及模擬開關使得電路結構復雜、編程麻煩,成本也未能降低。另一種是采用多通道高速逐次逼近型A/D轉換器,但16位以上的高速并行A/D轉換器通常為單通道或2通道,且價格昂貴。要實現多路(6路以上)信號同時采樣,則需要多片ADC,使得成本大大增加。

以上兩種方法采用的ADC的轉換速度通常在10μs甚至5μs以下,對于工頻電參數測量實際上有些浪費,在ADC轉換速度能夠滿足采樣頻率和數值處理要求的條件下,分辨率、線性度、抗干擾能力及量化噪聲等指標對于測量精度顯得尤為重要。本文設計采用一種基于6通道獨立采樣的16位串行Σ-ΔA/D轉換器AD73360L,構成多路相互關聯信號同時、同步采樣的數據采集系統,并且具有跟蹤輸入信號頻率變化,抗混疊濾波的功能。內部6個通道可同時采樣,無須CPU干預,從而有效地減少了由于采樣時間不同而產生的相位誤差,非常適合三相電壓、電流的采樣,且高達64kHz的采樣率完全能夠滿足電力參數測量要求。AD73360L還能多片級聯使用,使模擬量輸入通道的最大數目方便地擴展至48路。另外,AD73360L還有內置的程控可變增益放大器, 增益可在0~38dB之間選擇,因而它既適合于大信號的應用,也適合于小信號的應用[1]。

本文詳細介紹AD73360L與TMS320LF2407 DSP組成的同步采集系統的工作原理及不同結構的同步串行口的接口電路設計方法。

1 同步數據采集系統硬件結構與工作原理

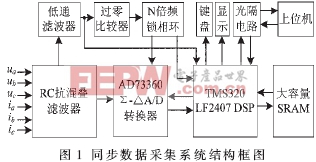

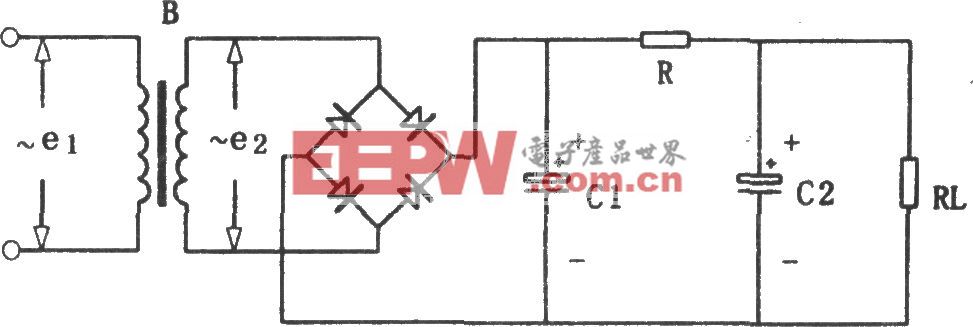

同步數據采集系統由三部分組成,其結構框圖如圖1所示。第一部分由抗混疊濾波電路和Σ-△A/D轉換器AD73360L組成,6路輸入信號經過RC抗混疊濾波處理后進入6通道Σ-△A/D轉換器。第二部分是由低通濾波器、過零比較器和倍頻鎖相電路組成的同步采樣信號發生電路。它產生N倍于測量信號頻率的方波信號作為采樣信號,控制A/D轉換器同步采樣和數字濾波。第三部分由DSP、SRAM、鍵盤、顯示和光隔控制等電路組成,實現對A/D轉換結果的高速讀取、數據處理、存儲、顯示和上傳數據給上位機等。

1.1 Σ-ΔADC內部結構與工作原理

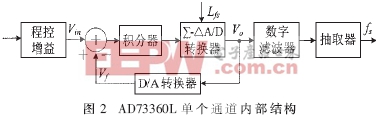

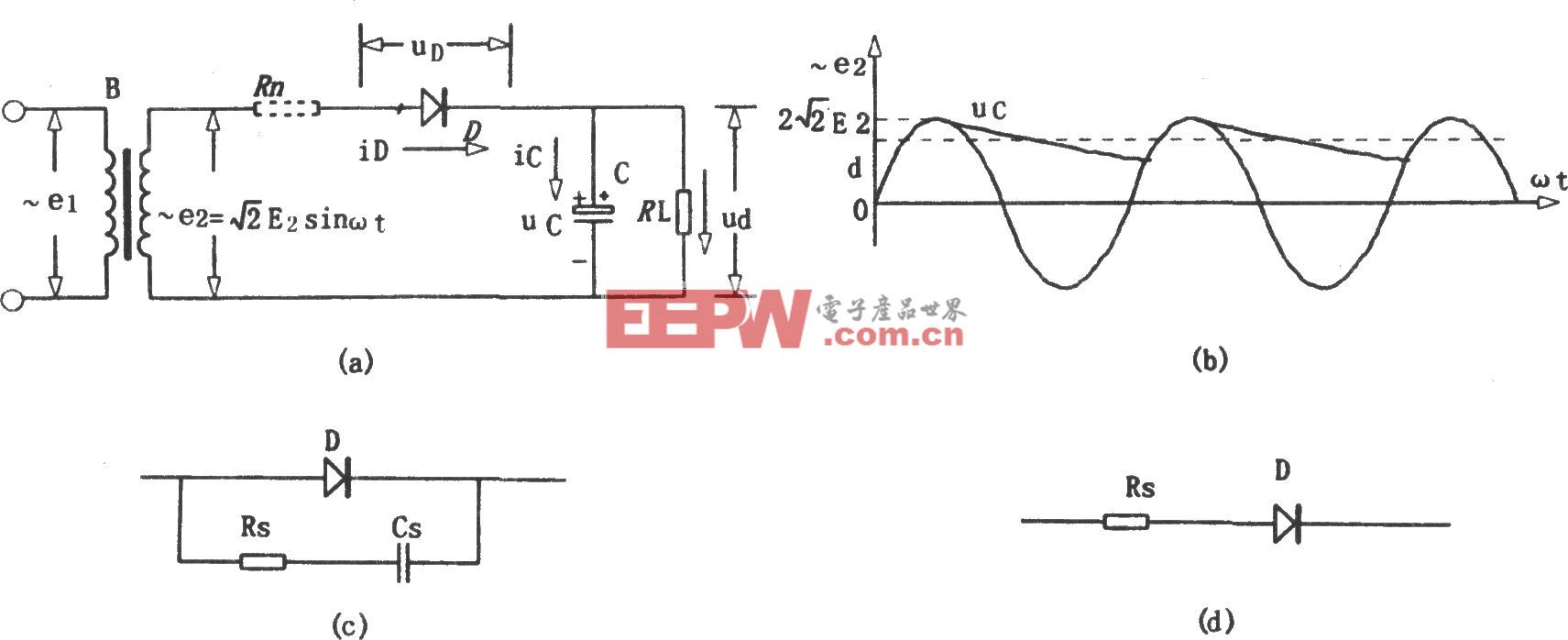

AD73360L的每個獨立的A/D轉換通道的內部結構如圖2所示。經程控放大器調理后的輸入信號Vin與反饋信號Vf相減后的增量再經采樣保持器保持后輸入A/D轉換器,低分辨率A/D轉換器以Lfs=DMCLK/8的高過采樣率對保持后的增量進行高速采樣,16位累加器對低分辨率采樣值累加求和后得到高分辨率的Vo,再由D/A轉換器轉換成16位模擬量Vf反饋到減法器,從而形成閉環負反饋的Σ-ΔA/D調制器。通過負反饋環路的不斷調整使Vo(N)=Vo(N-1)+[Vin-Vf (N-1)],即Vo(N)=Vin。由于A/D轉換器在量化過程中存在量化誤差,但通過閉環負反饋環路的誤差補足性能和高速重復取樣方法,把量化噪聲延續到Lfs/2的整個頻帶范圍內,并將它推到正常采樣率以外的高頻段上[2]。

抗混疊數字濾波器對2K個高速采樣值Vo進行數字均值滑動濾波(抽取系數K=高過采樣率/采樣率),濾除二分之一采樣頻率以上的高頻噪音和輸入信號的高次諧波。濾波特性的詳細描述參見文獻[1]。經濾波后的采樣值按K:1抽取作為輸出,降低了A/D轉換通道的采樣率,從而降低了同步串行口的速度要求。A/D轉換通道的采樣頻率fs=Lfs/K。時鐘頻率與高過采樣率、采樣率和抽取系數K均存在整倍數關系,提供了控制Σ-ΔADC實現同步采集、跟蹤濾波的條件。

1.2 同步采樣的實現方法

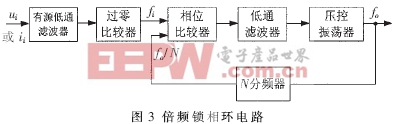

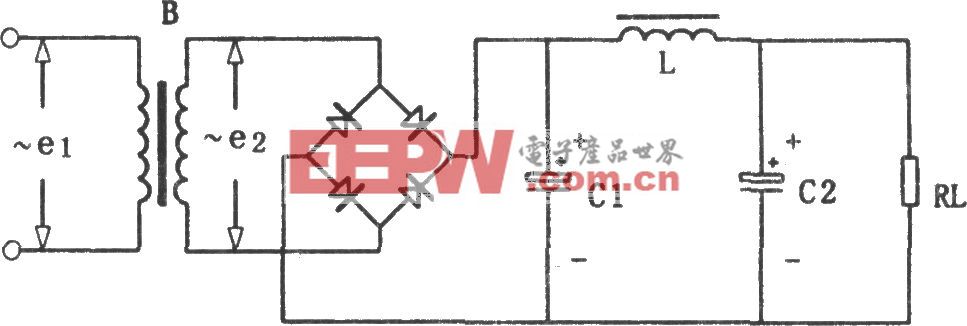

當采樣速率是被測信號頻率的整倍數,采樣點包含整個周期,且滿足采樣定理時,用DFT頻譜分析,頻域不會發生泄漏,可完全消除誤差[2]。因此采用硬件鎖相環電路產生整倍于被測信號頻率的方波來控制Σ-ΔA/D轉換器實現同步整周期采樣。倍頻鎖相電路如圖3所示。

為使鎖相環準確鎖定在被測信號(ui或ii)的基波頻率上,輸入電壓信號經3階有源低通濾波器濾除60Hz以上高次諧波,經過零比較器輸出對稱方波,作為高速鎖相環的輸入信號fi。fi同時也用作DSP測量信號頻率的信號源。

被測信號頻率fi與反饋信號fo/N進行相位比較,其相位差信號經過低通濾波后,控制壓頻振蕩器輸出頻率fo發生相應的變化,再經N分頻后反饋到相位比較器,通過負反饋環路的快速調整,最終達到環路鎖定。鎖定時fo/N與fi的頻率之差趨于零,即fo=Nfi。將鎖相環產生的倍頻信號fo作為Σ-ΔA/D轉換器的主時鐘信號,可以控制Σ-ΔA/D轉換器實現同步數據采集[3-4]。

被測50Hz信號每周期采樣1 024次,則采樣率fs為51.2kHz,壓控振蕩器中心頻率fo=fs×256=13.1 072(MHz)。壓控振蕩器上、下限頻率設計為16MHz和10MHz,當被測信號在60~40Hz范圍變化時,可以實現同步數據采集。同步采樣率可通過編程選擇每周期采樣1 024、512、256和128次。

鎖相環電路由高速鎖相環芯片74HC4046A和分頻器CD4060組成,產生AD73360L采集觸發信號,74HC4046A壓頻振蕩器最高輸出頻率可達24MHz。

1.3 跟蹤濾波的實現方法

由于Σ-ΔA/D轉換器實現同步采集,采樣頻率始終是被測信號頻率的整倍數。由Σ-ΔA/D轉換器的原理可知,抗混疊數字濾波器對2K個高速采樣值Vo進行數字均值滑動濾波,濾除被測信號中二分之一采樣頻率以上的高次諧波。因此,抗混疊數字濾波器的截止頻率始終跟蹤信號頻率變化,使它具有良好的抗混疊跟蹤濾波功能。

1.4 模擬輸入前端電路設計

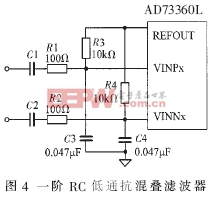

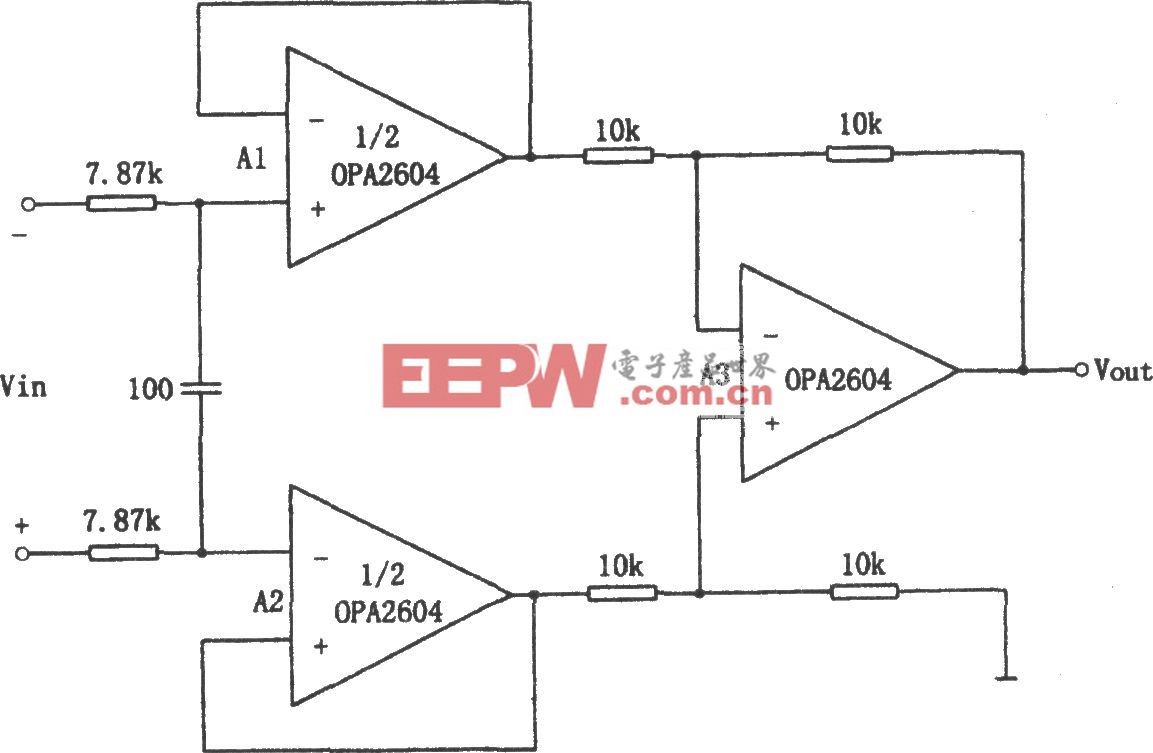

由于采用Σ-Δ A/D轉換原理,具有良好的內置抗混疊性能,所以對模擬前端濾波器的要求不高,用一階RC低通濾波器就能滿足要求[5],從而省去由開關電容濾波器和復雜外圍控制電路組成的抗混疊跟蹤濾波電路,節省了成本。為了提高系統抗干擾能力,模擬輸入通道采用差動輸入方式,具體電路如圖4所示。輸入信號通過C1和C2耦合到ADC的模擬輸入端。R1和C3、R2和C4構成一階低通抗混疊濾波器。圖中REFOUT是片內基準電壓輸出,通過R3和R4為輸入端引入共模偏置電壓,可根據需要配置為1.5V或2.5V。該電路可以把50Hz的交流信號直接耦合到AD73360L的模擬輸入端。

1.5 頻率測量方法

電壓或電流信號經濾波整形后輸入到鎖相環的方波信號fi,也同時輸入到DSP的CPI捕獲輸入端,利用DSP的捕獲功能,檢測兩個相鄰脈沖上升沿的時間間隔,計算出信號的頻率。為提高測量精度,每次檢測出N個相鄰上升沿的時間間隔,求平均得信號頻率。

2 TMS320LF2407與AD73360L接口電路設計

2.1 AD73360L性能簡介

AD73360L是ADI公司推出的6獨立通道的16位串行可編程A/D轉換器。每個A/D轉換通道由程控放大器、高過采樣率的Σ-ΔA/D調制器、抽取數字濾波器等組成。具有設計簡便、結構緊湊、工作穩定和可以方便地在幾種采樣率之間選擇等優點。與并行接口相比,采用串行接口的硬件連接線大為減少,這樣不僅可以減少印制電路板的面積,還可以減少電磁干擾,從而使系統更加穩定地工作。在不影響系統工作速度的條件下,在系統設計中利用串行接口代替并行接口不失為一種很好的設計方法。

2.2 AD73360L同步串行口

AD73360L的16位同步串行口(SPORT)有輸入、輸出兩個移位寄存器,它用6條通訊總線實現發送采樣值和接收控制信息的雙向同步通訊。它只能工作在主控方式。AD73360L的SPORT有三種工作模式:編程模式、數據模式和混合模式。

評論