LabVIEW FPGA模塊實現FIFO深度設定

為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設定不當帶來的數據不連續問題,結合LabVIEWFPGA的編程特點和DMA FIFO的工作原理,提出了一種設定FIFO深度的方法。對FIFO不同深度的實驗表明,采用該方法設定的FIFO深度能夠比較好地滿足系統對數據連續傳輸的要求。研究結果對深入展開研究和工程設計具有一定的指導意義。

本文引用地址:http://www.j9360.com/article/194725.htm引言

數據進入FPGA的速率高于傳出的速率,持續的傳輸會造成數據的溢出,斷續的傳輸可能會造成數據不連續。使用基于LabVIEW FPGA的DMA FIFO作為主控計算機和FPGA之間的緩存,若DMAFIFO深度設置的合適,FIFO不會溢出和讀空,那么就能實現數據輸出FPGA是連續的。

本文在介紹了LabVIEW FPGA模塊程序設計特點的基礎上,結合DMA FIFO的工作原理,提出了一種設定FIFO深度的方法,解決了FIFO溢出、讀空的問題,實現了數據的連續傳輸。實驗結果表明該方法正確、可行,程序設計滿足系統對數據傳輸連續性的要求。

1 LabVIEW FPGA模塊

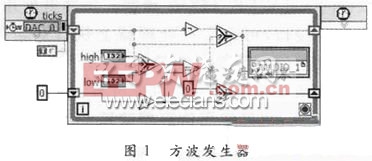

LabVIEW FPGA是LabVIEW的一個子模塊,使用該模塊可以通過圖形化的編程對NI公司RIO(Reconfigurable I/O)設備上的FPGA進行配置。圖形化的程序直接在硬件上實現,通過對RIO設備上的I/O接口的控制,可以靈活地對I/O信號進行分析和處理,表現出比固定I/O硬件更加優異的特性。使用LabVIEWFPGA模塊開發出來的系統具有開發周期短、結構模塊化、升級方便等優點。例如,圖1表示了一個用LabVIEW FPGA模塊設計的程序,在FPGA上實現方波發生器。該方波發生器通過數字接口DIO_1輸出方波,其占空比和周期可調。LabVIEW FPGA模塊在程序的設計與實現上都展現出了極大的靈活性。

1.1 LabVIEW FPGA程序開發流程

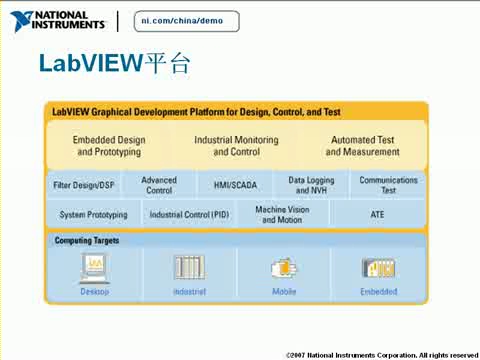

使用LabVIEW FPGA模塊開發應用程序的流程如圖2所示。首先創建FPGA vi,之后用FPGA設備仿真器在主控計算機上運行程序,反復地調試、修改,直至程序正確無誤。然后編譯FPGA vi,并把程序下載到FPGA上。FPGA部分的程序完成后,再根據需要在主控計算機上創建用戶界面程序Host vi,最終就完成整個系統的設計。

FPGA設備仿真器的打開方法是:首先在“項目瀏覽器”窗口中的打開“我的電腦”子菜單,右擊子菜單中的“FPGA Target”并在快捷菜單中選擇“Execute vion”下一級子菜單中的“Development Computer with Simulated I/O”。然后再在FPGA vi中點擊“Run”按鈕,這時程序在FPGA的設備仿真器上運行。

1.2 開發FPGA vi

發應用程序的第一步是創建用于配置PXIe-5641R板載FPGA的程序。在FPGA vi中可以實現算法邏輯,包括信號同步,定制數字通信協議,板載控制和預警處理判決機制等功能。通過LabVIEW FPGA模塊,可使用LabVIEW開發環境和許多類似的功能。但是由于FPGA不支持浮點操作,所以LabVIEW FPGA模塊較之LabVIEW完整Windows版開發軟件缺少了一些操作符和分析函數。另外,由于PXIe-5641R板卡沒有硬盤和操作系統,因此不支持文件I/O和ActiveX功能。LabVIEW FPGA模塊的函數面板如圖3所示。

硬件對象不管是FPGA設備還是FPGA仿真器,都可以訪問LabVIEW FPGA函數。仿真器使用RIO設備的I/O接口,可在主機處理器上執行邏輯算法。檢驗vi設計中的一些簡單性錯誤,避免不必要的反復編譯,尤其是在程序比較大的時候可節省大量的時間,提高編程效率。也可使用仿真器驗證vi的執行流程,但無法驗證硬件的確定性,若需要驗證硬件性能的確定性,必須對FPGA vi進行編譯。與其他FPGA開發工具一樣,根據應用程序的復雜程度和計算機資源的不同,編譯步驟可能要花上幾分鐘到幾個小時的時間。

評論