可以處理6.4Gbps以上數據率的創新型串行總線測試方

在高端運算(先進的微處理器)和消費電子(圖形和游戲芯片組)設備中采用的半導體器件一般通過高速串行總線接口提供高達6.4Gbps的數據率,例如PCI Express 和 HyperTransport。根據2005年的國際半導體發展路線圖(ITRS),到2010年,10Gbps以及更高速率的接口將被廣泛采用。而業界一些專家預測在10年內,數據率將高達20Gbps,因此一些基本方法必須改變。遠端環回是一種極具成本效益的創新技術。通過有效地幫助半導體廠商降低測試成本并縮短新一代半導體的開發周期,遠端環回必將加速上述發展趨勢。

本文引用地址:http://www.j9360.com/article/193660.htm目前高性能集成電路方面正在發生的架構改變將影響半導體產品的方方面面,包括從設計到終測和封裝。這一變化背后的驅動因素有兩個:(1)不斷增加的數據帶寬需求;(2)功率管理方面的需求。這兩方面的需求正在驅使設計師對出入IC的數據傳輸方式作出根本的改變。

設計工具和制造工藝已經改進到可用邏輯門數量已經不再是片上系統(SoC)性能的限制因素了。相反,性能限制因素主要是向芯片“內核”傳送數據的速度,以及功率管理和熱管理。過去,可以通過增加并行總線帶寬來傳送較大的數據量,但這種方法在功耗、引腳數量、封裝以及PCB成本等方面都有缺點。

實際上由于互聯層之間的電容和電感特性,在現有的并行總線上傳輸高速數據時還面臨一些其它限制。當線上的數據率高達約1Gbps時,上升時間、抖動、通道間和分布式時鐘擺率特性等這些并行總線設計中固有的問題將開始成為關鍵的限制因素。

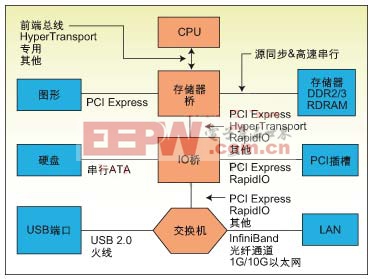

這些限制因素激勵著數據通信領域的數字設計工程師門在十年前就開始考慮串行技術。通過在為數不多的串行信道(圖1)上實現非常高的數據率,他們發現數據量和功率預算要求都能得到滿足。高速串行總線(HSSB)的很多物理性能與并行總線不同。主要的差別包括:

對于發送和接收等量的數據來說所需的連接點數量更少

串行總線為點對點連接,而傳統的并行總線則是多點對多點連接

串行總線為單向的數據通道,而傳統的并行總線則是雙向

串行總線的電壓擺幅小,可以支持更高速率的數據傳輸

串行總線采用差分信號,克服了影響低電壓擺幅的共模噪聲

與傳統的并行方式相比,串行的定時和數據捕獲方式有根本不同

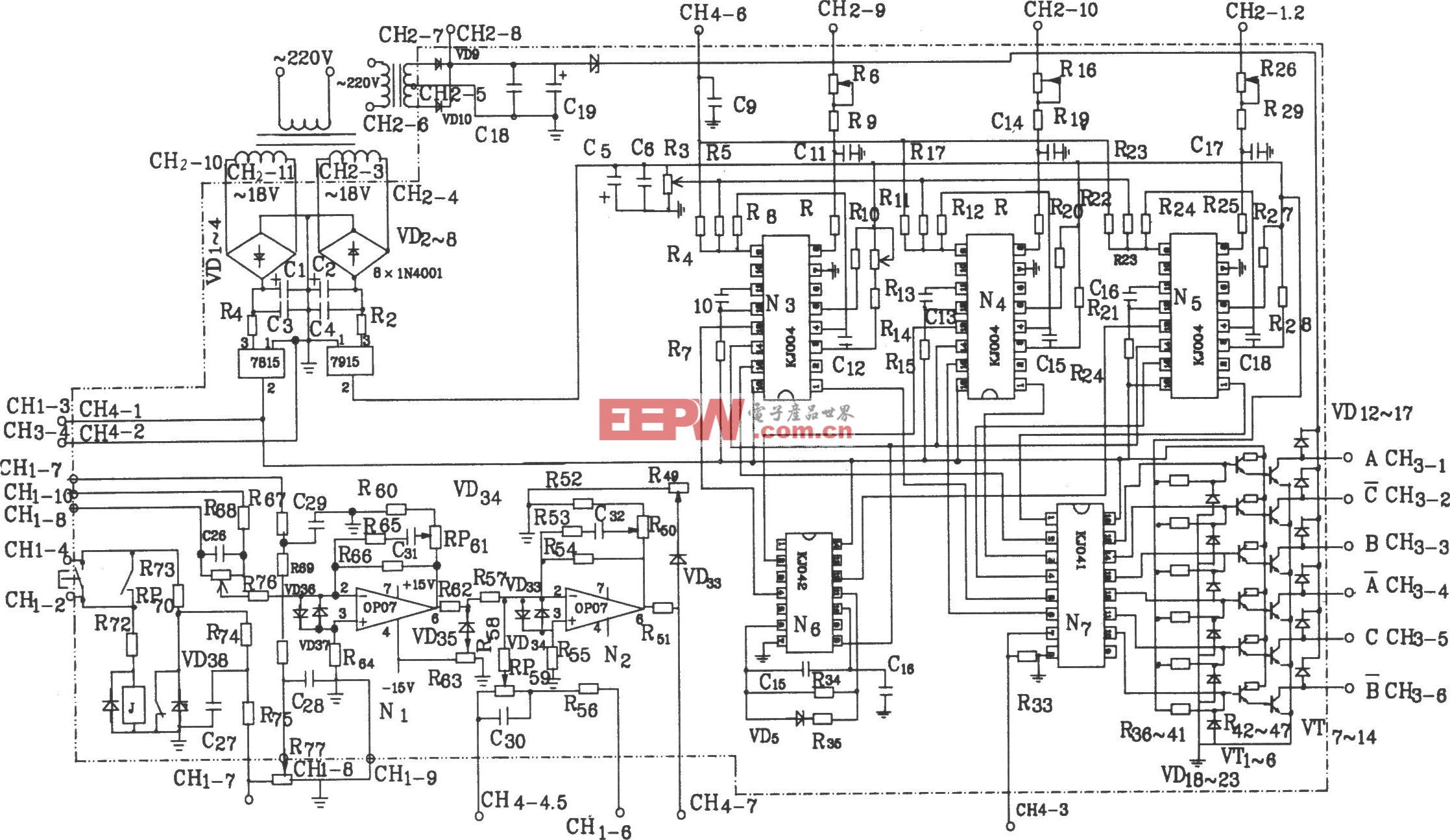

圖1:采用高速串行總線的PC架構。

高速測試方面的挑戰

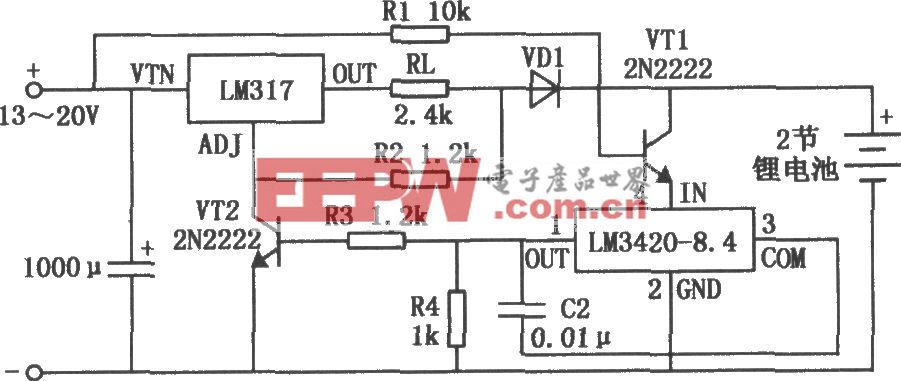

在以不是太高的成本通過HSSB提供這些呈指數式增長的傳輸速率方面測試公司將扮演關鍵的角色。像PCI Express I和II、HyperTransport 2.0和3.0、XAUI、XDR、RapidIO以及 InfiniBand這些高速接口將被越來越多地用來提供更高的數據率(圖2)。但是,高速數據總線帶來了一些很大的測試挑戰,在這里,傳統的功能測試和簡單的可測性設計(DFT)方法學不再適用。在高端自動測試設備(ATE)平臺上的傳統“功能”測試流程能夠提供很全面的測試覆蓋,但這些經過生產驗證的方法存在較大的缺點,比如成本較高,測試編程復雜。此外,每個引腳的成本隨著高速數據應用中總線速率的升高而升高,這也使得傳統的功能測試方法漸不可行。

圖2:到2010年數據率將超過10 Gbps,因此測試行業需要創新的測試方法來克服高速總線方面的挑戰。

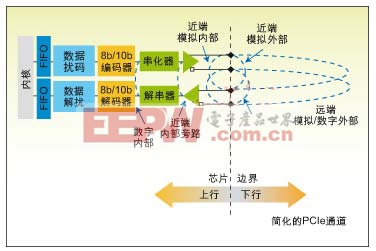

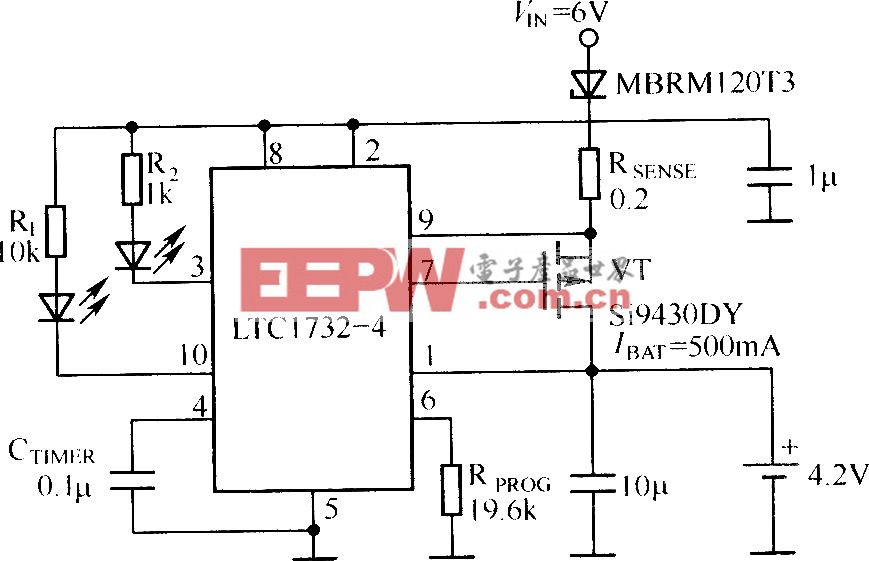

于是制造商們又轉向能夠實現更全面和成本優化的高速總線測試的環回技術(即:利用設備本身提供測試數據然后接收返回到設備的數據進行確認)。圖3 給出了一個簡化的PCI Express通道以及可能不同的環回位置,從有助于晶圓探測的純內部環回點,到被測器件(DUT)外面的環回位置。環回測試非常有效,不過實現的方式也非常重要,因為要考慮高速信號的典型損耗預算。損耗預算決定了可接受的信號劣化的程度,它通常需要考慮三個因素,即發射器,接收器和內部互聯,所有這幾項都將劣化信號的“眼圖”,從而影響測試覆蓋率。

圖3:在簡化的PCI Express單通道中可能的環回位置。

迄今為止,像“近端環回”這類替代性DFT技術已經為高端消費電子和運算應用方面的測試設備帶來了良好的成本效益(通過ATE中的簡化編程和降低投資)。目前的近端環回技術簡單并具成本效益,不過在解決像抖動、信號變化以及導致測試不完整甚至漏測的協議性能等問題方面卻無能為力。近端環回技術可以通過在I/O引腳之間創建通路而被設置到被測器件中。但是,在覆蓋率方面,其固有的低成本和簡單性將大打折扣。它沒有參數測量,缺乏信號控制,具有較低的與信號完整性或誤碼相關的故障發現概率等。例如,一個簡單的內部環回,或負載板環回,將使一個邊際接收器“隱藏”在強健發射器的陰影中,并通過環回測試。在較低的速率上都存在這些不確定性的時候,如果許諾3Gbps以上的覆蓋率將是冒險的方式。于是,半導體制造商需要尋找新的DFT技術來對影響器件和系統性能的關鍵變量實現靈活全面的測試。

遠端環回的優點

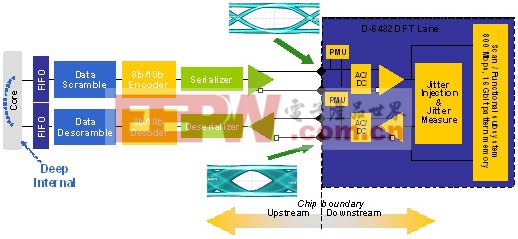

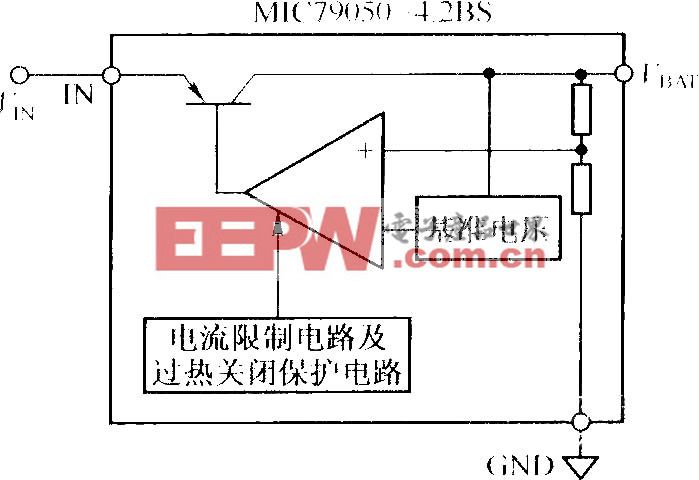

處于兩種極端之間,像遠端環回這樣的創新技術將DFT的靈活性與較深入的功能測試診斷結合在一起。這種遠端環回在Credence Systems公司的Sapphire D-6432DFT儀器中得到了有效實現。Sapphire D-6432DFT儀器是業界首套高速串行總線方面的集成測試解決方案。該方案結合了全速環回測試、抖動測量、注入測量,還有掃描/功能測試以及直流參數測量,所有功能都位于一個單獨的插件中。更好的是,它提供了帶有可編程信號劣化功能的遠端環回,這為測試工程師賦予了很大的靈活性,使得他們可以將DUT DFT/圖形產生器插入到盡可能遠的上游端。其結果是實現了更高的測試覆蓋率(與其他環回方法相比)。圖4中顯示的是利用DUT主圖案(master pattern)產生器在一個單獨的PCI Express通道上的一個簡單實現,其中D-6432DFT提供遠端環回。

圖4:利用內部DUT DFT實現數據包產生、帶可編程信號劣化功能的遠端環回可以完成高速通道的端到端測試。

D-6432DFT提供了比同類產品高四倍的密度,為制造商提供了一項突破性的DFT方法,從而大大減少了半導體器件的總成本和上市時間。與需要數倍投資卻僅能測試有限幾個通道的其他方案不同,D-6432DFT整合了大量的功能,可以在一臺儀器上測試多達16個環回對。這套儀器是與微處理器制造商Advanced Micro Devices (AMD)公司合作制造的,該公司的工程師們將獲獎的Sapphire平臺與D-6432DFT整合在一起,加快了該公司最新型產品的測試時間和上市時間。各地生產線上在用的D-6432DFT儀器已有200多套,這些儀器基于驗證過的Sapphire平臺,其全球用戶數量已達上百個。

利用D-6432DFT可以使DUT與智能的測試設備通信,從而首次實現了高速總線的生產級測試。測試工程師在編程信號劣化性能以便器件的發射和接收通道留出更多余量方面具有很大的靈活性,還能夠在一個具有成本效益的生產環境中實現抖動容差和抖動傳輸方面的測試。

這類環回提供了以下一些重要優點:

提供了能夠側重電壓和時間域眼圖的信號控制

增加了對信號完整性和誤碼靈敏度的測試覆蓋

儀器中整合了抖動注入和抖動測量

覆蓋了損耗預算所有的三個部分

接收和發射通道可以被用來向內核邏輯和協議棧提供測試向量

可以訪問器件引腳實現全面的直流參數測試

很明顯,呈指數式增長的總線速度給電路板的設計到生產帶來了根本轉變。重要的是要記住絕大多數器件都還有其他一些信號,甚至符合傳統接口標準的其它總線。一些器件同時使用幾種由不同協議和信令規范支持的高速總線已經是常見的事情了。實際上,正是技術和時間域的結合才使得這些器件功能如此強大,也使設計、調試和測試變得更加困難。在快節奏環境中,通過提供創新產品和解決方案來幫助用戶以更低的成本和更低的風險進一步優化和加速他們的最新測試技術,測試公司將扮演重要的領導角色。

評論