軟硬件搭橋改善SoC驗證效率

隨著系統級芯片(SoC)的復雜度不斷提高,軟、硬件開發融合所帶來的挑戰已經不可小覷。這些功能強大的系統現在由復雜的軟件、固件、嵌入式處理器、GPU、存儲控制器和其它高速外設混合而成。更高的功能集成度與更快的內部時鐘速度以及復雜的高速I/O相結合,意味著提供正常運行、并經過全面驗證的系統比以前變得更難。

本文引用地址:http://www.j9360.com/article/192965.htm傳統上,軟件驗證和調試及硬件驗證和調試一直是兩個不同的世界。通常情況下,軟件團隊和硬件團隊各自為政,前者專注于編程模型內部的軟件執行,后者則在硬件開發框架內進行調試,其中時鐘周期精度、并行運行及調試數據回溯原始設計的關系是關鍵。理論上,經過全面調試后,軟件和硬件應無差錯地協同運行。但在實際環境中,無差錯協同運行的情況不多,正因如此,經常會導致關鍵成本上升及產品開發周期延誤。

為在合理的成本和時間范圍內實現更高的集成度,業界必須轉向新的方法:設計的洞察。換句話說,如果我們想能夠高效地持續驗證和調試這些系統,工程師們必須提前設計成能夠提供全面的系統視圖。其中的關鍵是能夠了解涵蓋硬件領域和軟件領域的各種行為之間的臨時關系。本文介紹了使用嵌入式儀器調試SoC的一種方法,說明了通過整合硬件調試視圖和軟件調試視圖,可以更快、更高效地調試整個系統。

構建測試臺

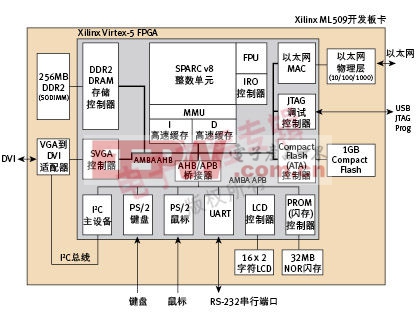

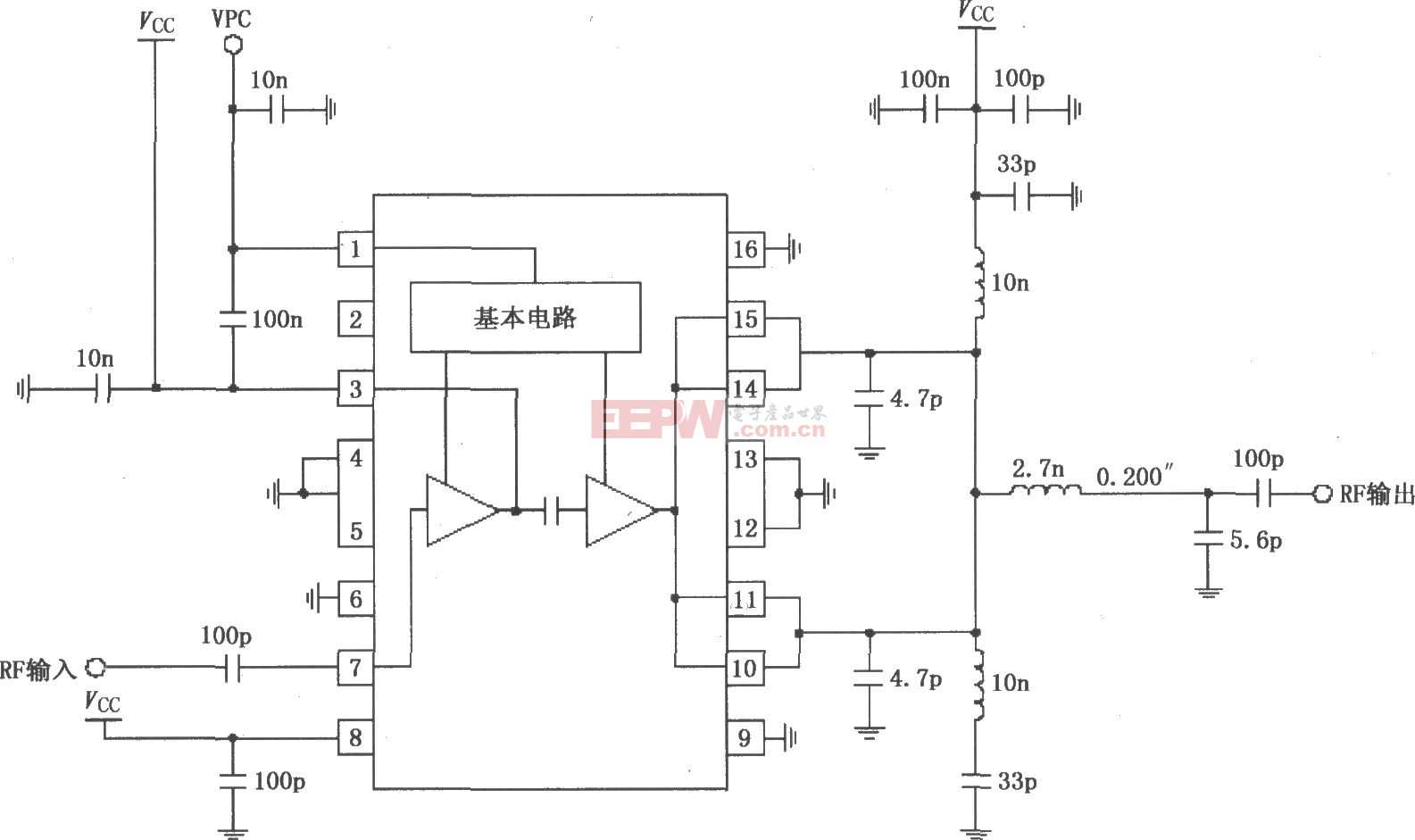

圖1所示的SoC由一塊32位RISC指令集處理器及一條AMBA APB外設總線組成,處理器連接到AMBA AHB系統總線上。SoC還包含一個DDR2存儲控制器、一個千兆位以太網網絡適配器、一個Compact Flash控制器、VGA控制器及多個低速外設接口。SoC運行Debian GNU Linux操作系統第4版,這一操作系統運行v2.6.21內核。處理器核心工作頻率為60MHz,DDR存儲控制器工作頻率為100MHz,其它I/O外設在33MHz~12MHz之間的基本頻率上運行。整個SoC在Virtex-5開發板卡上實現。

圖1. SoC基線測試臺。

總體上看,這一系統是一臺全功能計算機,能夠提供基于終端的用戶接入,能夠連接互聯網,運行應用程序,安裝文件系統等等。SoC的這些特點產生了復雜的調試場景,給硬件調試設施和軟件調試設施的功能帶來了壓力。在大多數情況下,關鍵操作都同時涵蓋硬件和軟件。

調試基礎設施

處理器核心開發人員一般會提供調試基礎設施,要么是某個核心的一套固定特性,要么是一群核心的可配置插件。不管是哪種形式,調試基礎設施都變成了被制造的核心的一部分。然后調試軟件使用這個基礎設施,為軟件開發人員提供調試特性。

與大多數現代處理器類似,如英特爾處理器、AMD處理器、IBM處理器、Oracle處理器和ARM處理器,這里突出顯示的處理器核心支持一套基本調試功能。在本例中,可以通過JTAG訪問的“后門”,允許軟件調試程序(如GDB)讀取和寫入系統中的存儲器,檢測處理器的運行狀態。通過這些機制及訪問原始軟件源代碼,GDB和其它軟件調試程序可以提供軟件斷點、單步操作、變量值檢查、堆棧跟蹤、初始條件配置、交替存儲器值及恢復功能。

在大多數情況下,硬件調試設施并不是與構成SoC的硬件IP核心一起提供的。相反,硬件調試設施通常疊加到現有的SoC設計上。造成這種差異的原因有很多。首先,與軟件調試不同,硬件要求的底層功能具有多樣化特點,通常只有在SoC組裝時才能得到全面了解。此外,每種新的SoC通常要求不同的調試基礎設施。最后,作為新興領域,硬件調試的標準化程度不高,生態系統建設不夠。因此,硬件調試設施通常被留給各個設計人員,這些設計人員會創建針對不同功能領域的特定調試特性。在大型機構中,通常會開發擁有內部支持的工具和結構。但是,隨著SoC的復雜程度不斷提高,創建高效硬件調試設施的復雜程度也在不斷提高,內部開發工作難以為繼。

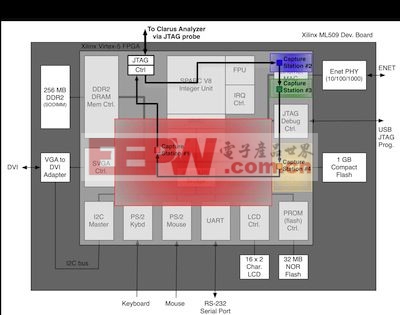

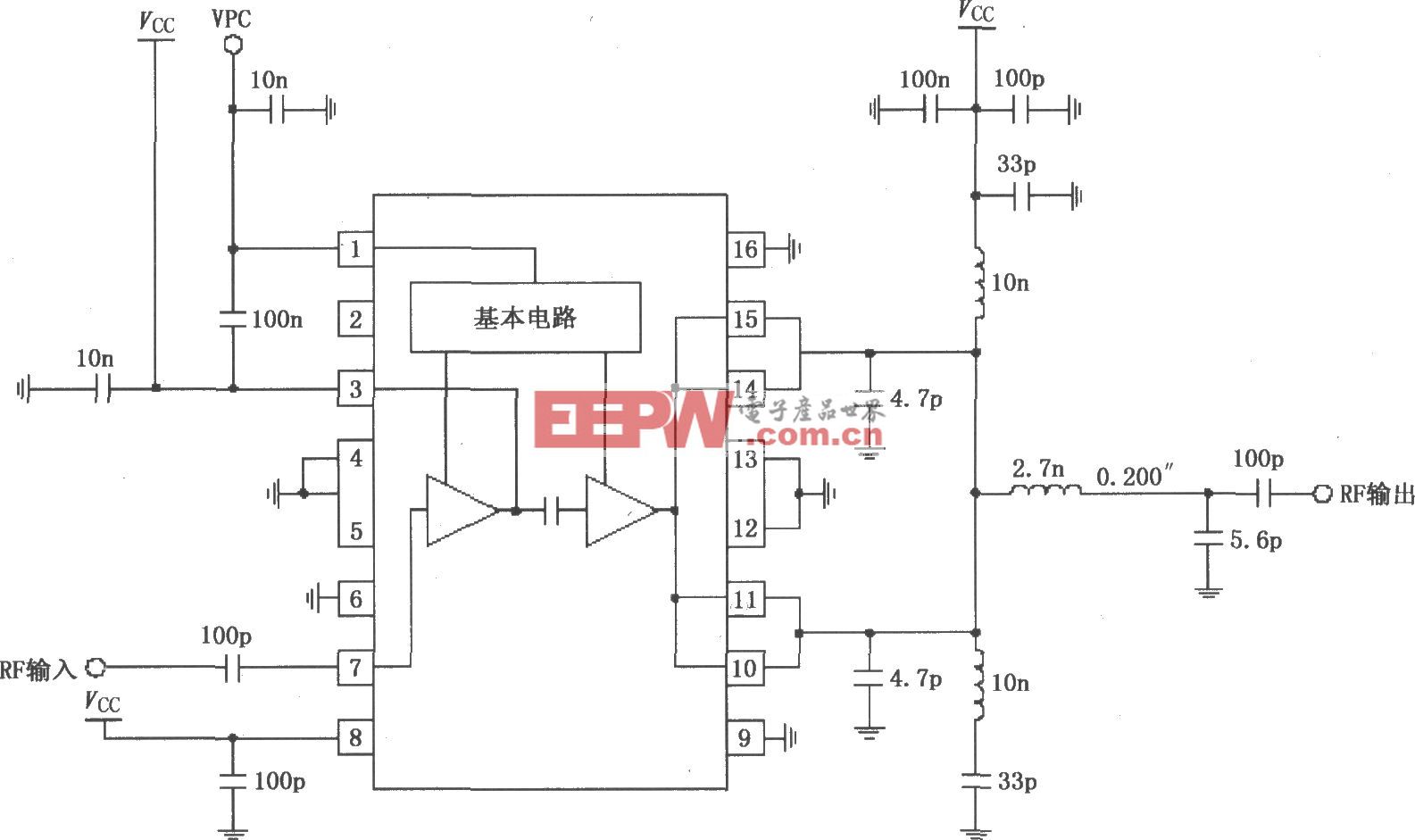

作為替代方案,測試和測量廠商可以提供完整的設計工具、IP庫和工作流程,創建硬件調試設施。圖2所示的設置稱為Tektronix Clarus Post-Silicon Validation Suite,這一驗證套件由多種可以重復配置的嵌入式儀器組成,這些儀器可以連接起來,分布在整個SoC中,創建滿足特定功能要求的調試基礎設施。Implementer工具可以在RTL級(Vreilog、System Verilog和VHDL)把硬件設計中任何層級的任何信號儀器化。Analyzer通過JTAG或以太網連接,配置和控制嵌入式儀器。最后,Investigator把嵌入式儀器收集的數據向回映射到原始RTL(在仿真環境中),實現更復雜的調試。

圖2: Clarus Post-Silicon Vlidtion Suite套件的結構。

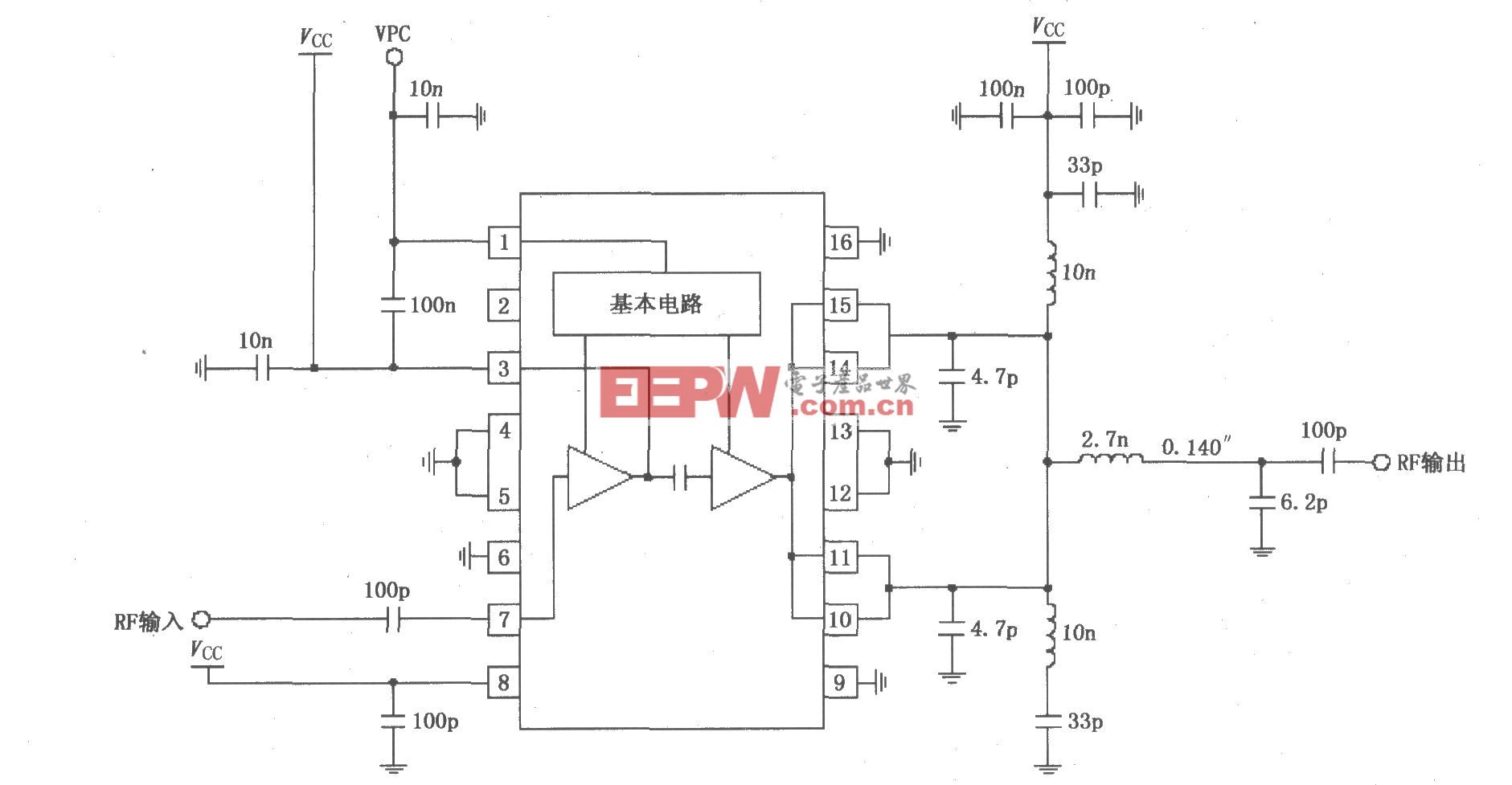

嵌入式儀器被應用到SOC中,提供調試基礎設施,如圖3所示。其中一個重要方面是能夠在調試過程中重新配置儀器,針對SoC不同領域中的各種信號和場景。基本儀器稱為捕獲站,其獨立管理觀測數據的選擇、壓縮、處理和存儲。多臺捕獲站通常一起使用,為某個SoC創建特定設計基礎設施。在插入過程中,捕獲站配置一系列關心的潛在信號、最高同時觀測數量以及最大RAM容量。捕獲站一般被分配給特定時鐘域,同時捕獲觀測數據。Analyzer從每個捕獲站中收集數據,顛倒壓縮算法,把每個站中捕獲的數據對準,在所有捕獲站中生成時間相關的視圖。

圖3: 硬件調試基礎設施。

評論