基于DDS頻率源的設計與實現

摘要 介紹了DDS的基本工作原理,闡述了DDS技術局限性,最終實現了一種基于FPGA+DDS可縭編程低相位噪聲的頻率源,輸出信號范圍170~228 MHz。測試結果表明,該頻率源具有高頻率分辨率和低相位噪聲等特點,能夠滿足通信系統對頻率源的設計要求。

關鍵詞 DDS;頻率源;AD9912;FPGA

頻率源是現代射頻通信系統的核心,對系統的運行起著決定性作用。射頻電路頻率源的好壞關系著整個系統的穩定性。目前頻率合成技術正朝著雜散和相位噪聲更低的方向發展,同時還要求有更寬的頻帶和更高的頻率分辨率。直接數字頻率合成(DDS)正是在該需求背景下發展的,其具有微小的頻率調諧和相位分辨能力。融合了模擬和數字技術的DDS是產生高質量高頻譜純度寬頻帶頻率的理想方法。

文中基于ADI公司的AD9912芯片提出一個直接頻率合成方案,輸出頻率范圍為170~228 MHz,頻率步進12.5 kHz,相位噪聲優于98 dBc /Hz@1kHz。

1 DDS基本工作原理

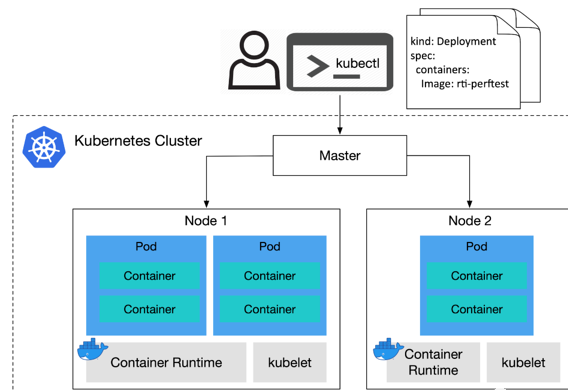

直接頻率合成器DDS是一種高分辨率的數字分頻器。通過頻率調節字來分頻系統時鐘,以輸出所需的頻率。DDS有兩個特點:(1)工作在數字域,其輸出頻率相位和幅度可在數字處理器的控制下,精確、快速地變換。(2)頻率分辨率主要取決于頻率調節字的位數,因此可達到較高的頻率分辨率。DDS基本原理框圖如圖1所示,其主要包括:相位累加器、相位-幅度變換器、數/模變換器和低通濾波器。

1.1 相位累加器

對于正弦波而言,幅度不是線性變化的,而相位卻是線性變化的,這便是DDS能夠合成正弦波的基礎。DDS依據頻率調節字的位數M,將0°~360°的相位變化平均分成2M等份。假設系統參考時鐘為fc;輸出頻率為fout在每個時鐘周期轉過一個角度360°/2M,則可產生一個頻率為f/2N的正弦波的相位增量。因此,只需選擇恰當的頻率調節字K,使得fout/fc=K/2M,即可得到輸出頻率。

fout=(K×fc)/2M (1)

可以得到DDS的最小頻率分辨率為

△f=fc/2M (2)

1.2 相位幅度轉化器

根據相位累加器的輸出,得到所需合成fout頻率所對應的相位信息,是將累加器輸出的數字相位信息變換成正弦波相應的幅度值。將正弦波相位到幅度的轉換可通過查表操作完成,然后正弦波幅度數值以二進制的形式被送入DAC進行數模轉換。

1.3 DAG數模變換器

從相位幅度轉換器得到的二進制數字信號被送入數模轉換器中,變換成模擬信號輸出。此處DAC變換器的位數對輸出頻率的分辨率并無影響,但DAC變換器的位數應將不低于二進制數字信號的位數,這樣輸出頻率的分辨率主要由頻率調節字的位數決定。

2 DDS的局限性

2.1 輸出頻帶范圍有限

由于DDS內部DAC和波形存儲器(ROM)的工作速度限制,使得DDS輸出的最高頻有限。目前市場上采用CMOS、TTL和ECL工藝制作的DDS芯片,工作頻率通常在幾十~400 MHz。設計采用的AD 9912芯片,其支持的最高時鐘高達1 GHz,根據奈奎斯特采樣定理,每周期的采樣點≥2,則其輸出的最高頻率≤500 MHz。實際上,為保證輸出波形的質量,實際采樣點>2,因此AD9912能夠輸出的最高頻率400 MHz。

2.2 輸出雜散大

由于DDS采用全數字結構,從而不可避免地引入了雜散輸出。DDS雜散輸出的來源有3個:相位累加器相位舍位誤差造成的雜散;幅度量化誤差造成的雜散和DAC非理想特性造成的雜散。

評論