數字控制幅頻特性測試儀的技術研究

摘要:文章以ARM微處理器為核心,采用直接頻率合成技術,設計了一種低頻高精度的幅頻特性測試儀。系統以直接數字頻率合成器AD9851作為掃頻信號源,用真有效值轉換芯片AD637實現對被測網絡的幅頻特性的測量,經ARM采樣與處理,最后得到被測網絡的幅頻特性曲線。實驗結果表明,本系統不僅能實現各種測試功能,而且測試頻率能提高到8MHz。因此本系統為現代電子科研實驗室提供了一種高精度和有較高實用價值的低頻幅頻特性測試儀。

關鍵詞:幅頻特性;直接數字頻率合成;真有效值;模/數轉換

0 引言

電子測量中,我們經常會遇到對網絡的阻抗和傳輸特性的測量。幅頻特性就是重要的傳輸特性之一,它也是各種電路系統及電子儀器的重要性能指標,是一個網絡性能最直觀的反映。幅頻特性測試儀被廣泛應用于電子工程等領域,尤其是模擬和高頻、射頻電子線路中。

傳統的幅頻特性測試儀大多是用LC電路構成的掃頻振蕩器,其結構復雜、體積龐大、價格昂貴、功能單一、操作不便、性價比較低。其方法是在一系列規定的頻率點上,逐點測量網絡增益,從而確定幅頻特性曲線。用這種方法得到的幅頻特性曲線比較精確,但其缺點是操作繁瑣、工作量大、容易漏測某些細節,不能反映出被測網絡的動態特性。而現有的幅頻特性測試儀也不能很好地滿足用戶的需求,要么存在設備體積大、易有故障、并且操作復雜等缺點,難以滿足尤其是現場自動測試的要求,要么就是結構復雜、價格昂貴、維護困難。因此,對于數字化、智能化、高性能幅頻特性測試儀的需求量日益增大,基于此原因本文設計了基于ARM的數字幅頻特性測試系統。

1 系統方案實現

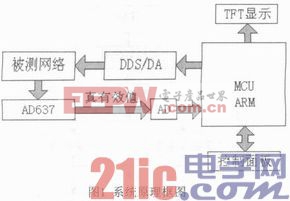

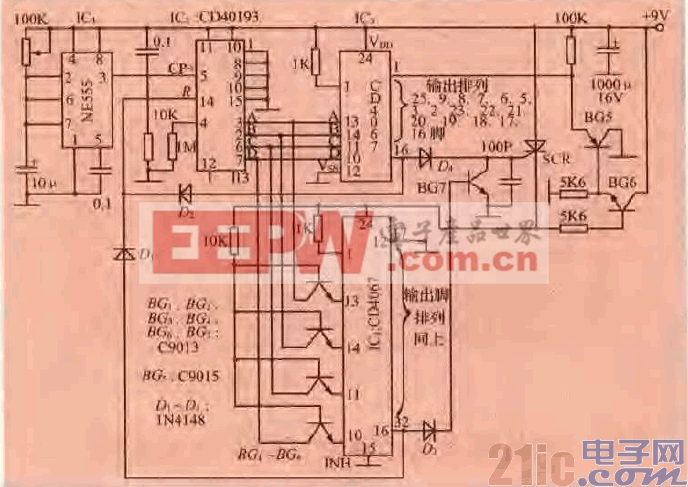

傳統的數字幅頻特性測量儀是通過測量頻率得到正弦信號的峰峰值,然后通過計算得到幅度。這樣為了保證A/D采樣的精度,一般在進入A/D采樣之前,需要對被測信號進行幅度調理,確保被測峰峰值在A/D采樣的電壓范圍內。另外,進入A/D進行采樣的信號必須滿足抽樣定理,即fs≥2fi,所以在進入A/D采樣之前必須用低通濾波器對其濾波,以防止頻譜混疊而影響測量結果。此方案具有抗干擾能力強、設計靈活、精度高等優點,但調試困難,A/D采樣困難且計算量大,增加了軟件難度。由于預先不知道被測網絡的頻響特性,故掃頻信號通過被測網絡后可能發生很多種未知的變化,本文采用集成真有效值變換芯片,直接輸出被測信號的真有效值。這樣可以實現對任意波形的有效值測量。系統框圖如圖1所示。

2 系統的硬件電路設計和軟件編寫

2.1 供電電路設計

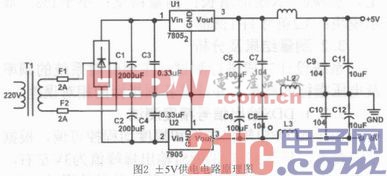

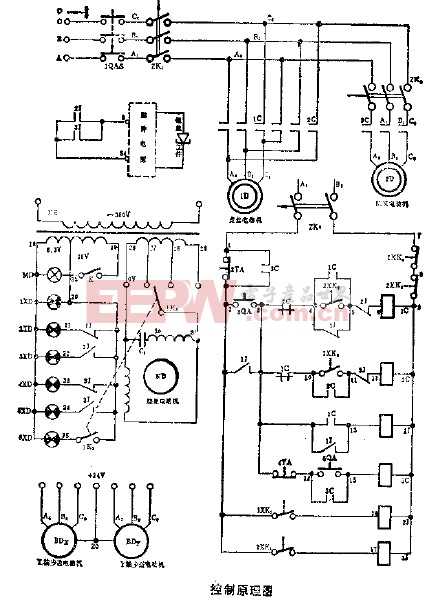

根據系統性能的要求,需要設計±5V和+3.3V的直流穩壓電源,而且要求電源的紋波應盡量的小,以減少對輸出信號的干擾。電源采用橋式全波整流、大電容濾波和三端穩壓器件穩壓的方法產生±5V和+3.3V直流電壓,固定輸出的三端穩壓芯片為LM7805和LM7905。穩壓管的輸出通過電容和電感濾波;數字部分與模擬部分用電感隔離,這樣就可以得到紋波系數很小的直流電壓,其中±5V供電具體電路如圖2所示。

2.2 掃頻信號電路設計

掃頻信號源在頻率特性測試儀中有著重要的地位,它的各項性能指標直接關系到整個測試系統所能達到的性能要求。其掃頻信號的中心頻率都應當是被測網絡通頻帶的中心頻率,掃頻寬度應稍大于被測網絡的帶寬。為此要求掃頻信號源的中心頻率及掃頻寬度均可獨立調節。而具有高集成度的DDS芯片AD9851內部包含高速、高性能D/A轉換器及高速比較器,可作為全數字編程控制的頻率合成器和時鐘發生器。外接精密時鐘源時,AD9851可以產生一個頻譜純凈、頻率和相位都可以編程控制且穩定性很好的模擬正弦波,這個正弦波能夠直接作為基準信號源。AD9851可直接與STM32接口,通過程序來進行控制。實際電路中,AD9851采用高速并行接口工作方式,STM32利用并行方式對AD9851進行控制,其頻率和相位控制字直接寫入數據輸入寄存器中。AD9851芯片采用±5V供電,外部時鐘采用30MHz晶體,內部寄存器控制6倍頻,信號輸出為恒流源。RSET引腳用來配置其內部D/A轉換器的滿度輸出電流值。從AD9851的數據手冊中可知,DAC滿幅輸出電流為Iout=39.93/ Rset。

低通濾波器相關文章:低通濾波器原理

網線測試儀相關文章:網線測試儀原理

評論