在系統可編程模擬器件ispPAC10及其應用

摘要:介紹lattice半導體公司推出的可編程模擬器件ispPAC10內部結構及設計應用。該控制芯片可方便的完成對信號的放大,衰減及濾波的功能。

一.引言

在20世紀末,Lattice公司推出了在系統可編程模擬器件(ispPAC――In-System Programmability Programmable Analog Circuits),將在系統可編程技術引入模擬電路的應用領域。與可完成邏輯功能的數字在系統可編程大規模集成電路(ispLSI)一樣,ispPAC它允許設計者使用EDA軟件在計算機上設計修改模擬電路,并進行仿真,最后還可以通過編程電纜將設計方案下載到芯片中去.sipPAC主要可以完成3個功能:1.信號調理。2.信號處理。3信號轉換。本文介紹的ispPAC10其功能是信號調理即能對信號進行放大,衰減,濾波。

二.結構與原理

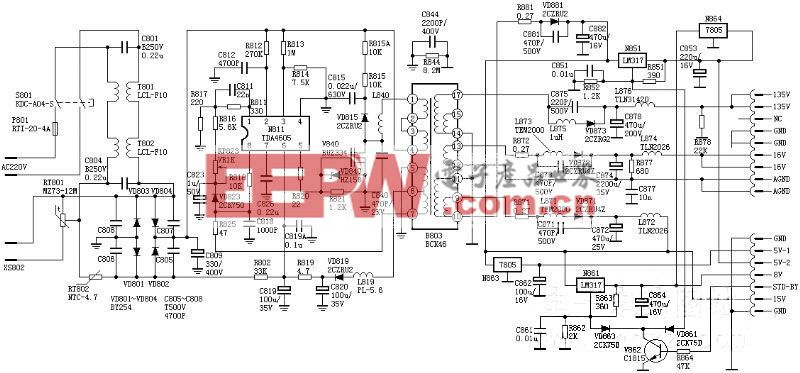

ispPAC10器件的結構由四個基本單元電路,模擬布線池,配置存儲器,參考電壓,自動校正單元和ISP接口所組成如圖1.0。器件用5V單電源供電。

其基本單元電路(PACblock)由一個差分輸出的求和放大器(OA)和兩個具有差分輸入的、增益為1至10以整數步長可調的儀用放大器組成。輸出求和放大器的反饋回路由一個電阻和一個電容并聯組成。其中,電阻回路有一個可編程的開關控制其開斷;電容回路中提供了120多個可編程電容值以便根據需要構成不同參數的有源濾波器電路。如圖1.2所示

三.主要功能指標

*4個儀表放大器增益/衰減能分級進行

*可編程的增益范圍(0~80dB)

*多達4個輸入的信號求和

*精確有源濾波(10~100KHz)

*器件可重復檫寫10000次

四.參考設計

(一). 增益設置

1.普通增益設置

通常情況下,PACblock中單個輸入儀用放大器的增益可在1至10的范圍內按整數步長進行調整。IA1和IA2是求和的關系,如果所求的增益在10之間,那就只需用其中一個。如圖1.3所示,將IA1的增益設置為4,則可得到輸出VOUT1相對于輸入VIN1為4的增益;

如果要得到增益大于20的放大電路,可以將多個PACblock級聯。圖1.4所示的是增益為40的連接方法。

2.分數增益的設置

除了各種整數倍增益外,配合適當的外接電阻,ispPAC器件可以提供任意的分數倍增益的放大電路。例如,想得到一個5.7倍的放大電路,可按圖1.6所示的電路設計。

評論