基于VHDL的I2C總線控制核設計

摘要:從狀態機的角度,介紹一種I2C控制核的VHDL設計方法。將其嵌入到FPGA中,用于實現與TMS320C6000系列DSP的接口,并配合DSP的軟件完成對視頻采集與顯示處理系統中數字視頻編、解碼器工作模式寄存器的配置及其狀態查詢。著重介紹I2C控制核的總體設計方案,詳細描述其內部命令狀態機和時序狀態機的工作原理及相應的VHDL代碼。此外,介紹I2C控制核與DSP相互通信中斷處理機制的VHDL實現方法。最后,給出在Xilinx公司的ISE6.1+ModelSimXE5.7c軟件平臺中進行EDA的綜合結果與時序仿真圖。 關鍵詞:I2C總線 狀態機FPGA VHDL DSP 控制器核 引言 I2C總線是雙向、兩線、串行、多主控(multi-master)接口標準,具有總線仲裁機制,非常適合在器件之間進行近距離、非經常性的數據通信。由于其使用兩線的硬件接口簡單,I2C總線的應用越來越廣泛。實現I2C總線通信協議主要有兩種方法:①利用MCU對兩根I/O口線進行軟件編程,模擬I2C總線的SCL和SDA時序要求;②使用專用I2C總線控制核,但受其主機(host)接口方式和時鐘頻率的限制,在有些場合應用并不方便。 1 總體思想 SCL和SDA分別為I2C總線的時鐘線和數據線。目前,支持I2C總線通信協議的視頻編、解碼芯片大多只支持100Kb/s或400Kb/s的傳輸速度,并且支持兩種地址:①從設備地址(SCLAVE ADDRESS,8bit),分為讀地址和寫地址,高7位用于選中芯片, 第0位是讀/寫控制位(R/W),決定是對該芯片進行讀或寫操作;②內部寄存器單元地址(SUBADRRESS,8bit),用于決定對內部的哪個寄存器單元進行操作,通常還支持地址單元連續的多字節順序讀寫操作。I2C總線的讀、寫操作過程如下。 寫過程(S:開始,Sr:重開始,P:停止,-S:從設備,-M:主設備,W:寫位,R:讀位)

讀過程

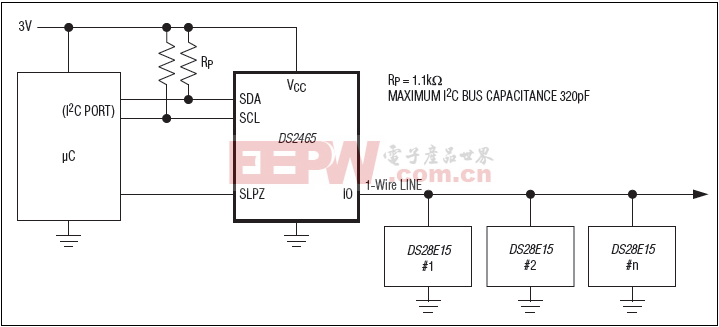

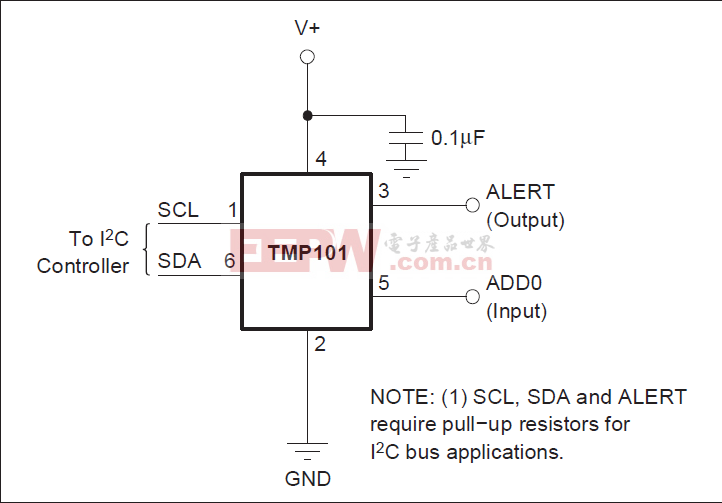

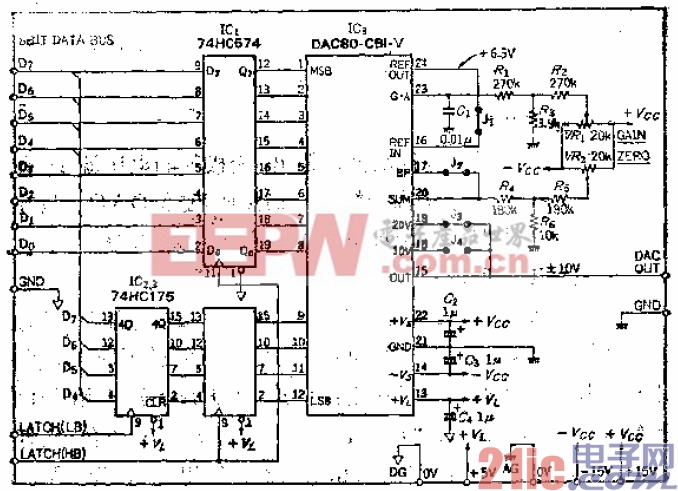

I2C控制核的設計采用自頂而下的方法,分為三個模塊:I2C_top模塊、I2C_cmd模塊、I2C_core模塊。總體結構框圖如圖1所示。I2C_top模塊是頂層管理模塊,主要任務是接收DSP發來的控制信號、命令及數據;發送由從設備讀出的數據和確認位到DSP;實現I2C控制核與DSP的中斷通信機制;提供當前I2C控制核的工作狀態;把DSP發出的命令字信號送到I2C_cmd模塊。 在設計I2C控制核時,必須注意以下幾個方面: ①I2C控制核與主機(Host,即C6711 DSP)以及視頻編解碼器的硬件接口連接關系。考慮到I2C總線通信協議的時序關系及芯片讀/寫操作過程,I2C控制核應該包括兩個外圍接口,如圖1所示。一是與C6711 EMIF(External Memory Interface,擴展存儲器接口)的高速異步存儲器ASRAM(Asynchronous SRAM)接口,稱為主機接口。它向I2C控制核發出控制命令與數據,0位地址總線、32位雙向三態數據總線、異步輸出使能信號aoe、異步寫使能awe、異步讀使能are、外部存儲器空間選通ce2、外部中斷申請eint。二是與視頻編/解碼器相連的I2C兩線接口SCL、SDA。I2C控制核稱為I2C總線的主設備(master),實現EMIF的ASRAM接口向I2C總線接口的轉化;I2C器件(視頻編碼器、視頻解碼器)被稱為I2CU叫線的從設備(slave)。

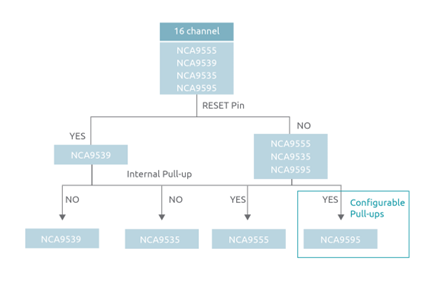

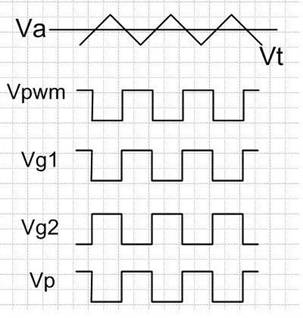

時鐘尺度寄存器(PRES)用于產生兩個時鐘頻率信號:pres(7 downto 5),用于產生I2C控制核的工作頻率fcore;pres(5 downto 0),用于產生I2C總線的時鐘SCL頻率fi2c。其計算公式如下: 其中:pres1=1+pres(7 downto 5) pres2=1+pres(4 dwonto 0) 由于eclk=100MHz,以pres(7 downto 5)=“100”=4,pres(4 downto 0)="10000"=16,則 fcore=100/[2(1+4)]=10MHz fi2c=10/[6(1+16)]=0.098MHz=98kHz≤100kHz 可以看出,這樣設備時鐘尺度寄存器容易實現100MHz~100kHz的轉變。 ③需要設置與DSP的相互通信的機制。由于C6711的CPU運行速度為150MHz,而I2C的速度僅為100Kb/s,為了不影響DSP程序的高速運行,采用中斷機制。當DSP發出讀、寫命令后,繼續執行自己的程序,而由I2C控制核完成命令后,I2C_top模塊負責向DSP發中斷請示eint。DSP在中斷服務程序中讀取SR,從RXR中讀數,并發出新命令到CR,發送新數據到TXR。 設計的核心工作是對I2C總線命令及時序的狀態劃分。在控制核內共設置了兩個狀態機,分別稱為命令狀態機和時序狀態機。其中,命令狀態機用于管理I2C總線上的命令狀態,如表1所列,并實現I2C總線具體的讀、寫操作的命令狀態轉移過程;時序狀態機用于實現I2C總線上啟動、停止、讀、寫、確認等命令的具體時序關系。這樣就把控制核從邏輯上分為兩個狀態機,共同完成最終的總線命令與時序。 2.1 命令狀態機 命令狀態機是I2C_cmd模塊的核心部分。該模塊的主要功能有兩個:一是把I2C_top模塊發送的start、write、read、stop四個命令信號轉化命令碼,發送I2C_core模塊;二是實現DSP發出和從slave接收到數據的串并轉換。 從I2C總線的通信協議中可以看出I2C總線上的信號可以分為空閑(IDLE)、啟動(START)、讀(READ)、寫(WRITE)、確認(ACK)和停止(STOP)六種工作狀態。在IDLE時,SCL和SDA都為高電平,從設備不斷檢測Start命令的出現。I2C控制核(即I2C總線的主設備)在接收到DSP發送來的Start命令后,主設備進入START狀態,并根據Read和Write命令,可以進入READ或WRITE狀態。由于主機的讀、寫操作都是以字節進行的,對應8個周期的I2C總線讀/寫操作,故設置一個8字拍的計數器,使得READ或WRITE狀態能維持8個SCL周期。在完成字節讀或寫操作之后,都將進入ACK狀態。進入ACK,標志一個DSP的讀/寫命令已經完成,因此發送中斷申請給DSP。在中斷服務程序中,DSP查詢狀態寄存器后,再發出下一個命令。這時I2C控制核,或者是轉移到IDLE,或者是轉移到STOP。命令狀態轉移關系如圖2所示。 2.2 時序狀態機 I2C_core模塊負責與視頻編碼器、解碼器的I2C接口,最終實現I2C總線信號SCL和SDA的啟動、停止、讀、寫、確認等具體操作的時序關系。其功能的實現主要由時序狀態來完成。根據I2C總線通信協議中SCL和SDA之間的時序關系,總線上包含兩種命令(Start/Restart,Stop)和兩種操作(Write,Read),時序關系如圖4所示。Start命令:在SCL為高電平時,SDA上出現一個下降沿。Stop命令:在SCL為高電平時,SDA上出現一個上升沿。Write操作:SDA只能在SCL為低電平時變化,在SCL為高電平時應保持不變。Read操作:只能在SCL為高電平時,對SDA進行采樣。 SCL在Start命令的A狀態時,保持原有電平不變,而在B狀態時變為高電平,這樣就可以實現Restart命令。系統時鐘信號eclk由時鐘尺度因子分頻,得到狀態轉移的同步時鐘使能信號(eclk_en)。在eclk和eclk_en的控制下進行狀態移轉,最后都轉移到空閑狀態(IDLE),并保持最后一個狀態時的信號電平。圖4中標注了每個命令的關鍵時刻。 3 中斷信號的處理機制 I2C控制核作為I2C總線的主設備,是在DSP的控制下工作的。它采用中斷機制與DSP通道。當一個讀寫命令完成后,主設備會向DSP發出一個中斷申請信號eint(上升沿有效)。在DSP的中斷服務程序中,置位命令寄存器的中斷響應確認位(i_ack_r='1'),使主設備清除其發出的中斷申請信號(eint='0'),而i_ack_r信號將在置位命令結束后的下一個時鐘上升沿自動清除。這樣,可以允許主設備發出下一個中斷申請。 begin if(nReset='0')then int='0';i_ack_r='0'; elsif(eclk'vent and eclk='1')then if(nce='0'andnAwe='0')then if(core_en='1'and eadd="001")then --寫入命令寄存器 i_ack_r=cr(7);--寫入'1' end if; else i_ack_r='0'; --自動清除 end if; int=cmd_done_ack and ien; end if; Eint=int and(not i_ack_r_;end process;命令碼 4 EDA綜合結果與結論 使用Xilinx ISE6.1對I2C核的VHDL描述進行綜合(synthesize)和實現(implement),目標器件采用Xilinx公司的高密度系統級FPGA-Virtex系列芯片v50cs144-6。設計的總體等效門數為1844門,系統時鐘的最大頻率為120.758MHz。圖5為使用ModelsimXE5.6a對在目標器件上布局布線后的VHDL模塊進行仿真(Simulate Post-Place Route VHDL Module)的結果。其中,edat信號上“10010000”中的“1”依次是啟動和寫命令;“01100001”中的“1”依次是停止、讀、中斷清除命令。從圖中可以看出,實現了從TMS320C6000 EMIF接口到I2C總線接口的轉換功能,并實現發中斷申請(eint=1)和清除中斷申請的功能,完成了I2C總線通信協議的啟動、寫、確認,讀、確認、停止操作的時序。 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||

評論