采用FPGA實現脈動陣列

微電子學的發展徹底改變了計算機的設計:集成電路技術增加了能夠安裝到單個芯片中的元器件數目及其復雜度。因此,采用這種技術可以構建低成本、專用的外圍器件,從而迅速地解決復雜的問題。

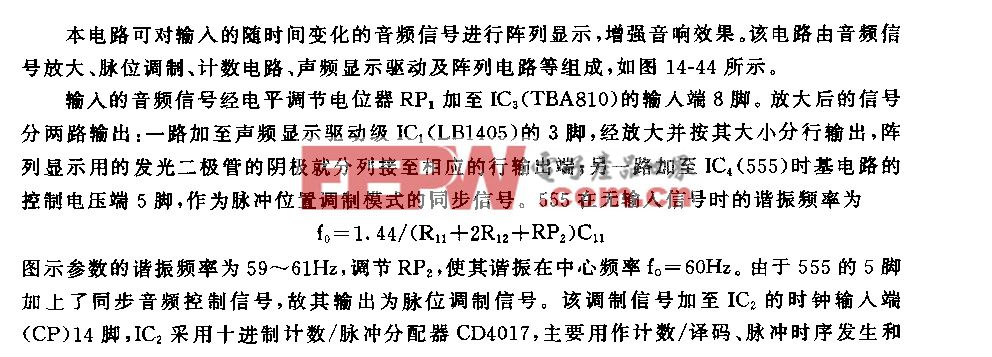

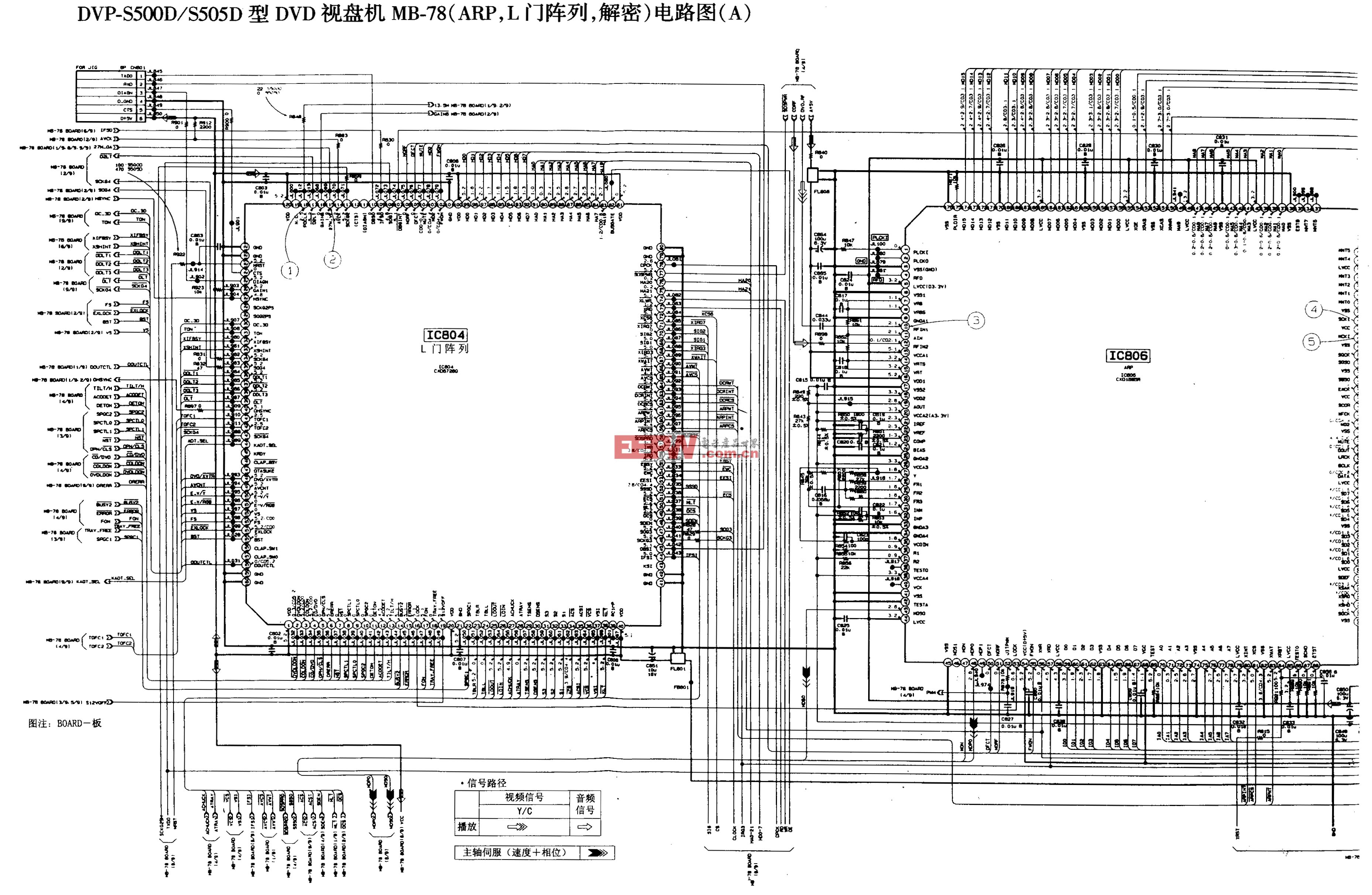

大規模集成電路(VLSI)技術明確地指出:簡單和規則的互連導致廉價的實現方式以及高密度,而高密度能夠實現高性能和低開銷。有鑒于此,我們致力于設計并行的運算法則,其擁有簡單且規則的數據流。我們也致力于將流水線技術作為在硬件中實現這些算法的通用手段。借助于流水線技術,輸入和輸出之間的處理可以同時進行,因此,總的執行時間變得最小。在流水線的每一階段上,采用流水線技術外加多處理技術能夠獲得最佳的性能。在下面,我們要論證一個微處理器陣列能夠借助流水線矩陣計算,使得速度得到最佳的提升。圖1是一個脈動陣列的簡單例子。在這種結構下有兩個輸入向量陣列,z和x。處理單元有一個值, ,通常是根據定義在單元內的運算法則而得到的結果。其輸出是一個向量, 。

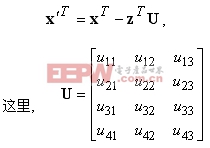

。

圖1中的脈動陣列的輸出可以被簡單地表示為向量矩陣關系:

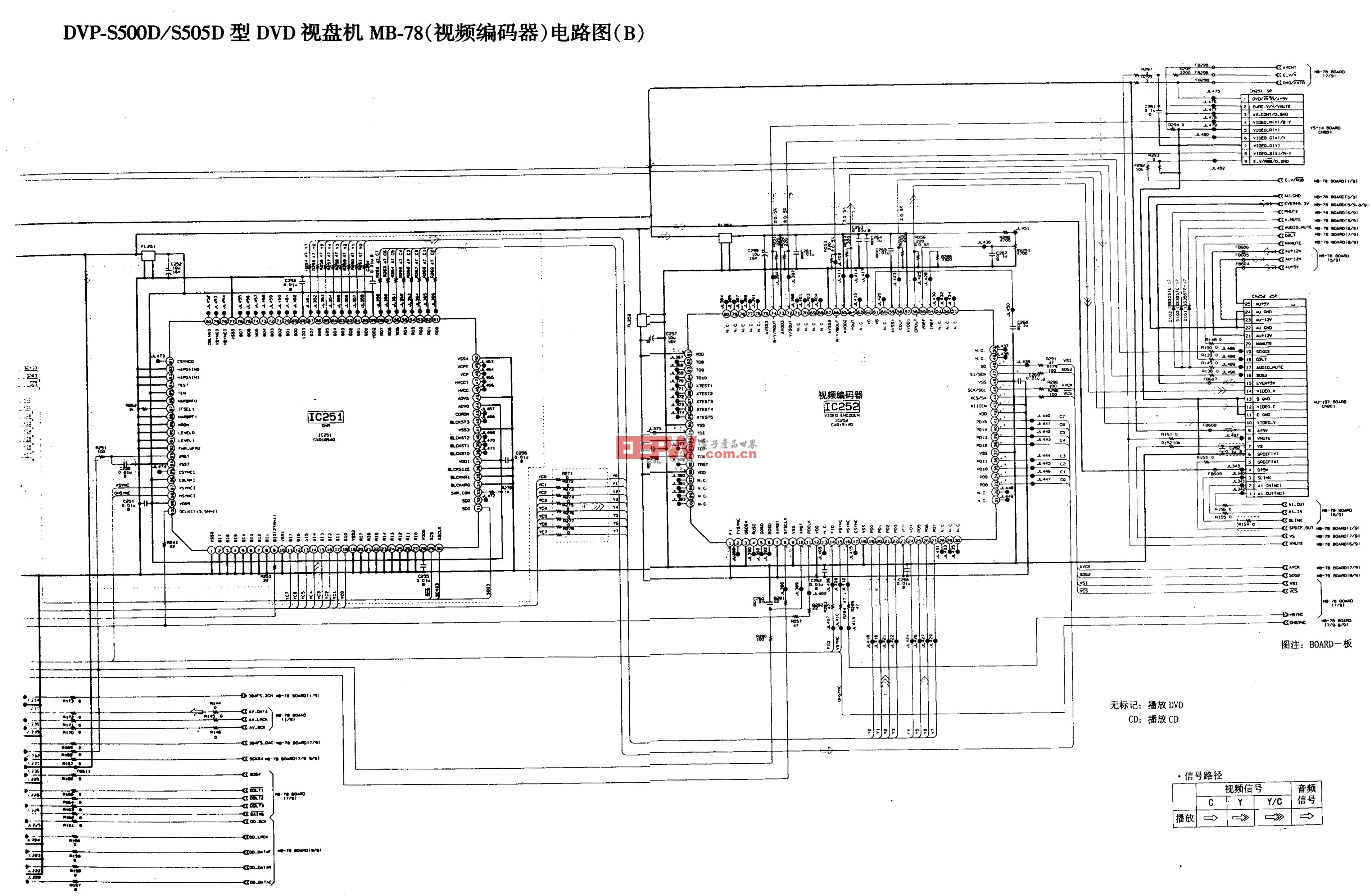

它顯示了如何采用一對脈動陣列來解決在很多信號處理情形 下出現的線性最小二乘問題。主陣列(三角形的)常用來實現Givens旋轉法 的流水線序列,其通過歸一化變換到上三角形,從而減小數據矩陣 。

重要的實時應用的數量在增長,尤其在無線通信領域,要求系統在出現強干擾的情況下可靠地工作。基于碼分多址(CDMA)技術的現代無線通信系統由于多路徑衰減、多址干擾(MAI)、碼間干擾(ISI)這三個主要因素造成容量和性能上的限制。克服這些困難的常用方案是采用發射功率控制、錯誤控制編碼以及典型地基于傳統耙狀接收機的多種技術。耙狀接收機的性能由于快速時變通道的出現而大打折扣,這些快速時變通道在實際的移動無線通信系統中是很常見的。有兩種干擾與用于CDMA下行線的耙狀接收機有關:一種是指間干擾(IFI);另一種是多址干擾(MAI)。這兩種干擾都是由于無線通道的頻率選擇引起的。當采用耙狀接收機時,IFI和MAI會使CDMA系統的容量受到限制。

改善CDMA傳輸的性能需要抑制IFI和MAI。當延遲擴散較大時,可以通過信道均衡,將頻率選擇性衰減信道轉換為頻率非選擇性衰減信道。這樣,基于自適應規則的均衡接收機似乎是一個有效的CDMA接收機。它通過復原正交擴頻碼來恢復發送的數據,從而抑制了IFI和MAI。自適應的最小均方(LMS)法和遞歸最小二乘(RLS)法迭代地計算時變信道。借助相對較短的存放數據的緩沖器,它們具有較短的處理延時的優點。RLS算法注重回溯到初始態的所有信息,根據到達的新數據更新加權向量的估計值。由于收斂性較好,因此RLS優于LMS。另外,如果自適應算法發散,或者收斂緩慢,它將很難實現對IFI和MAI的抑制,而這是均衡接收機非常基本的目標。另一方面,RLS算法需要在信號保持期間進行大量的運算,而這不是一個實際的無線電系統所期望的,因為簡化是降低成本的關鍵所在。在改進RLS濾波器的數字特性情形下,引入通過QR分解(QRD)得到的輸入矩陣的直角三角形。這樣的一個三角形化過程可以通過一系列的Givens旋轉法來實現,這種做法常被用來在基于樣本為單位的原理上實現QR的更新。

采用Givens旋轉法的QRD-RLS算法的一種有效的并行三角形脈動處理器陣列的實現方法已經問世 。一個統一的周期性時鐘控制著這個脈動陣列,它執行平面旋轉以消除輸入信號矩陣的一些元素。通常,旋轉角度的計算需要對開方、乘法和加法運算求逆。這種方法稱作基本的Givens旋轉法,但存在自由的Givens平方根 。CORDIC算法也可以僅僅采用二進制的移位和加法來實現,但是由于需要定標、更多的迭代以及計算中可能的不穩點而增加成本。圖2舉了一個常規的CDMA系統的例子。作為比較,圖3展示了一個構建出的RLS自適應均衡器。

評論