基于FPGA的線陣CCD數據采集系統

摘 要:本文介紹了一種基于FPGA的線陣CCD數據采集系統的實現方法。該系統在Altera的Cyclone EP1C6Q240C8上實現,使用SoPC Builder開發組件定制CPU軟核處理器和系統所需的IP模塊,CPU軟核處理器作為微控制器實現邏輯控制和數據采集功能,用硬件描述語言編程實現CCD驅動電路的設計。

關鍵詞:CCD;數據采集;Nios II

引言

CCD(Charge Coupled Devices,電荷耦合器件)具有光電轉換、信息存儲等功能,而且集成度高、動態范圍大、線性好、信噪比高,在很多領域都得到了廣泛應用。CCD有面陣和線陣之分,面陣CCD主要用于攝像、圖像處理、數據存儲和機器人視覺等領域;線陣CCD的應用也很廣泛,像光譜分析、測徑,測量微小位移等。

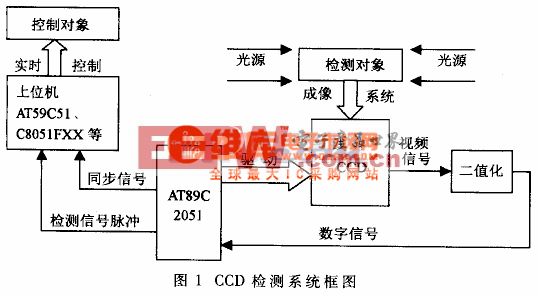

本文介紹了一種在FPGA片內利用SoPC技術實現的線陣CCD數據采集系統,系統中的CCD選用東芝公司的TCD103D,這是2592像元的二相線陣CCD;ADC選用TLC876,精度為10位,轉換速率20MSPS。整個系統在一片FPGA(EP1C6Q240C8)上完成,在Quartus II軟件中用硬件描述語言實現CCD的驅動電路和A/D采樣控制器的設計。使用SoPC Builder定制了一個32位軟核處理器作為微控制器,協調CCD驅動電路、A/D采樣控制電路之間的工作時序,完成數據采集、存儲等功能。系統分3部分:硬件電路、驅動電路和數據采集部分。

系統硬件設計

硬件平臺結構見圖1。系統中的UART和SDRAM Controller是SoPC Builder內建的IP核庫中的IP模塊,通過Avalon Bus和Nios II CPU相連。SoPC Builder能自動產生每個模塊的HDL文件,同時自動產生一些必要的仲裁邏輯來協調Avalon Bus上各功能模塊的工作。Nios II CPU是系統的核心,協調CCD驅動電路、A/D采樣控制電路之間的工作時序,完成數據采集、存儲和數據傳輸。SDRAM作為數據緩存器,軟件程序和配置文件存儲在外擴的Flash中。系統通過RS-232接口和計算機相連,接收計算機的控制命令。CCD工作時要求驅動脈沖的幅值在11V以上(典型值為12V),因此,CCD模塊包含一個電平轉換電路,將FPGA輸出的電平轉換成12V。

驅動電路設計

FPGA具有集成度高、速度快、可靠性好及硬件電路易于編程等特點,非常適合驅動電路的設計。CCD驅動電路和A/D采樣控制電路在Quartus II軟件中編程實現,產生CCD和ADC所需的工作時序。

CCD驅動電路設計

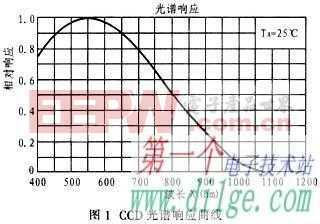

TCD103D是一種高靈敏度、低暗電流、2592像元的二相線陣CCD圖像傳感器。分辨率為11mm,它在4路驅動信號作用下輸出OS和DOS信號。正常工作時先輸出64個啞元信號,然后連續輸出S1~S2592有效像素單元信號。S2592信號輸出后,又輸出28個啞元信號,以后便是空驅動。DOS是補償輸出信號。4路驅動信號分別是轉移信號SH、兩相時鐘信號Φ1、Φ2 和復位信號RS。SH 的周期就是器件的光積分時間。

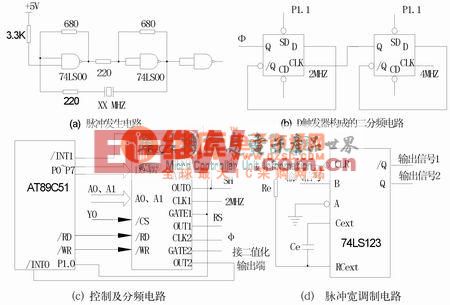

復位脈沖RS的產生

RS 是使輸出擴散二極管復位的復位管控制脈沖,復位一次輸出一個信號,脈沖占空比為1:3,典型頻率為1MHz。RS 由U1單元產生。如圖2所示,單元內兩個D觸發器構成一個環形計數器,CLK 為4MHz 的時鐘脈沖,經分頻輸出兩個1MHz、相差90的方波脈沖和,將這兩路脈沖經或非門輸出,即可形成RS脈沖。除RS脈沖外,U1單元還產生fai_base脈沖和AD_CLK脈沖。前者頻率為0.5MHz,占空比為1:1,用于產生時鐘脈沖信號。AD_CLK是ADC的采樣時鐘信號,頻率為1MHz。

時鐘脈沖Φ1和Φ2的產生

時鐘脈沖Φ1、Φ2的典型頻率為0.5MHz,相位相差180,為避免MOS電容中的信號電荷包向上/下2列模擬移位寄存器的電極轉移不完全的情況發生,要求Φ1、Φ2在并行轉移時有一個大于SH=1持續時間的寬脈沖。在圖3所示的電路中(圖中Φ1、Φ2分別用fai1、fai2表示),cnt12b是一個異步清零的加法計數器,當計數值至少大于1341(計數值由光積分時間決定),p1輸出高電平,開啟dec4b。dec4b是一個異步清零的減法計數器,輸出為1100時,立即產生異步清零信號,將兩個計數器全部清零,同時生成Φ1、Φ2所需的寬脈沖。

轉移脈沖SH的產生

SH是使MOS 電容中的信號電荷轉移到移位寄存器中的轉移柵控制脈沖。如圖3所示,dec4b的q3產生的寬脈沖經過一個下降沿觸發的DFF,波形滯后q3半個CLK周期,兩個信號作與運算,即產生SH脈沖。

EN是驅動電路的使能信號,EN為高電平時,電路工作。

A/D采樣控制時序的產生

TLC876以多級流水線結構原理設計而成,在每一個采樣時鐘的上升沿都啟動一次采樣,完成一次采樣,但從模擬值采樣到10位數字量輸出有5個時鐘周期的延遲。

采樣時鐘AD_CLK由U1單元產生,頻率為1MHz。采樣控制電路的作用是協調CCD和TLC876之間的工作時序。CCD正常工作時前后各有64和28個啞元信號,這 92 個啞元信號在 A/D 轉換時不需要采樣。但是,因為輸出信號有5個周期的延遲,實際應采2597個點。采樣控制單元的主要功能是:使能信號ENABLE有效后,模塊等待當前的積分周期結束,并在下一個積分周期開始時對前64個啞元信號進行計數,等64個信號全部移出后啟動采樣時鐘,ADC在AD_CLK控制下連續對信號進行采樣和輸出。

數據采集系統設計

Nios II CPU是系統的核心,協調各模塊之間的工作,實現數據采集功能。當計算機發出控制信號時,微處理器啟動CCD驅動電路和A/D采樣控制電路,CCD在驅動時序控制下將堆積的電荷導出并開始新的積分周期。A/D采樣控制電路等待當前積分周期結束后產生TLC876的采樣時鐘AD_CLK。AD_CLK和Nios II CPU的一個I/O相連,該I/O口定制時設置成邊沿中斷。因此,在每個AD_CLK的上升沿啟動一次采樣的同時產生一次中斷,通知CPU讀取轉換好的數據。CPU將讀取的數據暫存在SDRAM中,一次數據采集完成后,由微處理器將采樣控制器中的計數器清零并關閉采樣控制單元和CCD驅動電路。這部分采用C語言在Nios II的集成開發環境(IDE)中實現。軟件流程如圖4所示。

結語

本文提出了一種基于FPGA的線陣CCD數據采集系統的實現方法。該系統在Altera公司的Cyclone FPGA上實現,使用SoPC Builder開發組件定制系統所需的IP模塊,具有開發周期短、集成度高等特點。軟硬件均采用編程實現,設計靈活,在實際應用中收到很好的效果。

參考文獻:

1 饒程,袁祥輝.積分時間和頻率同時可調的線陣CCD驅動. 醫療衛生裝備.2005年第10 期.

2 仁愛鋒,初秀琴等.基于FPGA的嵌入式系統設計.西安:西安電子科技大學出版社,2004

3 TOSHIBA. TCD103D Datasheet

評論