CPLD通用寫入器設計與開發

摘要:可編程邏輯器件(ProgrammableLogicDevice,簡稱PLD)是20世紀70年代發展起來的一種新型邏輯器件,它是現代數字電子系統向超高集成度、超低功耗、超小型封裝和專用化方向發展的重要基礎。它的應用和發展不僅簡化了電路設計,降低了成本,提高了系統的可靠性和保密性,而且給數字系統的設計方法帶來了革命性的變化。CPLD(ComplexProgrammableLogicDevice),即復雜可編程邏輯器件,它是20世紀90年代初期出現的EPLD改進器件。同EPLD相比,CPLD增加了內部連線,對邏輯宏單元和I/O單元也有重大的改進。Xilinx是世界上最大的可編程邏輯器件供應商之一,FPGA的發明者。產品種類較全,主要有:XC9500/4000,Coolrunner(XPLA3),Spartan,Vertex。在本文中,我們將通過對CPLD的發展、結構、應用和設計等方面的認知,了解CPLD的基本原理,并設計出CPLD脫機編程寫入器的電路圖。

關鍵詞:復雜可編程邏輯器件CPLD(ComplexProgrammableLogicDevice),現場可編程邏輯陣列器件FPGA(FieldProgrammableLogicArray),電子設計自動化EDA(ElectronicDesignAutomation),硬件描述語言HDL(HardwareDescriptionLanguage)。

一.CPLD及其功能

可編程邏輯器件包括現場可編程門陣列FPGA(FiledProgrammableGateArray)和復雜可編程邏輯器件CPLD(ComplexProgrammableLogicDevic)這兩種類型。

具有固定數目輸入和輸出的任何組合邏輯函數可以在可編程只讀存儲器PROM中以輸出為輸入的查找表方式來實現,許多實現組合邏輯的結構變型已從這一簡單的概念引申出來,而利用VLSI的密度產生更通用的能實現PCB板上幾個簡單PAL互連功能的器件是PAL/PROM這類范例的擴展,稱為PAL構造的PLD,即復雜可編程邏輯器件――CPLD。

CPLD所提供的邏輯資源比較少,最高約一萬門。但是,CPLD提供了以下特殊功能:

1.CPLD在設計過程中為客戶提供了更大的靈活性,因為對于CPLD來說,設計反復只需要改變編程文件就可以了,而且設計改變的結果可立即在工作器件中看到。CPLD不需要漫長的前置時間來制造原型或正式產品,CPLD器件已經放在分銷商的貨架上并可隨時付運;

2.CPLD不需要客戶支付高昂的NRE成本和購買昂貴的掩膜組,因為CPLD供應商在設計其可編程器件時已經支付了這些成本,并且可通過PLD產品線延續多年的生命期來分攤這些成本;

3.CPLD允許客戶在需要時訂購所需要的數量,從而使客戶可控制庫存。采用固定邏輯器件的客戶經常會面臨需要廢棄的過量庫存,而當對其產品的需求高漲時,他們有可能為器件供貨不足所苦,并且不得不面對生產延遲的現實;

4.CPLD甚至在設備付運到客戶那兒以后還可以重新編程。正是由于有了可編程邏輯器件,一些設備制造商現在正在嘗試為已經安裝在現場的產品增加新功能或者進行升級。

二.Xilinx公司的XC9500系列可編程邏輯器件

近年來,可編程邏輯器件在高密度、高速度、低功耗等方面發展很快。在CPLD方面,Xilinx公司推出了高性能、低成本的XC9500[tm]系列,以及在單個器件內結合了極低功耗和高速度、高密度和多I/O引腳特點的CoolRunner[tm]系列。此系列CPLD器件需要的功耗極低,并且價格低廉,從而使其對于成本敏感的、電池供電的便攜式設備(如移動電話和數字手持助理)非常理想。

XC9500系列CPLD器件是Xilinx公司具有代表性的產品,圖1為XC9500系列芯片的外觀圖:

圖1XC9500系列芯片的外觀圖

三.CPLD的設計與開發

XC9500系列可編程邏輯器件的內部結構以及時序問題就不一一介紹了,我們下面所關心的是CPLD的設計與開發。

CPLD器件的設計一般可以分為設計輸入、設計實現、設計仿真和下載編程4個步驟:

1.設計輸入

設計輸入就是將設計者所設計的電路以開發軟件要求的某種形式表達出來,并輸入到相應的軟件中。

2.設計實現

在設計輸入之后,實現工具把邏輯映射到目標器件結構的資源中,決定邏輯的最佳布局,選擇邏輯與I/O功能塊連接的布線通道。Xilinx設計實現工具以極高自動化程度完成這些任務,設計編譯實用程序自動地恢復所有的輸入文件,執行所有必要的步驟來產生CPLD的配置程序。

3.設計仿真

這一部分的最大功能是便于用戶查看自己的設計思想是否得到實現。我們可以在設計的過程中對整個系統乃至各個模塊進行仿真,如果有問題,可以很方便地修改錯誤,而不必在硬件上動手腳。仿真不消耗資源,不浪費時間,實乃可編程邏輯器件設計與開發精髓之所在。

4.下載編程

下載編程一塊是將設計階段生成的JEDEC文件裝入到可編程器件中,是本文的重點。器件編程需要滿足一定的條件,如編程電壓、編程時序和編程算法等。普通的CPLD器件需要一種編程專用設備(編程器)完成器件編程。

Xilinx商提供基于IEEE1149.1,JTAG協議(JTAGBoundaryScan)的CPLD編程寫入器。它由DSUB

―25接口和下載電纜組成,被開發的CPLD必須在開發基板上進行編程,板上就必須留有JTAG使用的接口(TMS,TCK,TDI和TDO信號線等)。這樣的好處是我們能夠實機調試。

除Xilinx的實機編程器外,還可設計脫機CPLD編程寫入器(電路如圖2),它能對CPLD進行編程寫入,而不需要開發實物基板,實物基板設計時就不需要留有JTAG接口。這樣能節約基板,減少產品體積。圖2的設計電路有以下幾個主要的部件:

1.并行接口

在圖2中,我們可以看到一個Parallel并行接口,用它經過數據線和計算機連接。其實在這里,我們

圖2CPLD編程寫入器總電原理圖

圖3Parallel并行接口圖

也可以使用其它接口,例如Multilinx/Serial串行接口,以及Multilinx/USB接口等。這里使用的端口也是我們經常用于連接本地打印機的接口。該接口是具有25Pin的接口,它的各Pin端口的信號如圖3所示。

2.Bus/Buffer電路

JTAG的信號,如TMS,TCK,TDI和TDO均需要設置Bus/Buffer電路。該Buffer電路采用了三態電路,這樣的設計使得CPLD寫入器對計算機的并行接口無不良影響,僅在需要對CPLD寫入器進行數據輸入輸出時才動作。在不輸入輸出信號數據時它處于高阻狀態,在需輸入輸出數據時才處于低阻狀態,保

證對CPLD寫入,讀出所需電流。Bus/Buffer電路如圖4所示:

圖4Bus/Buffer電路

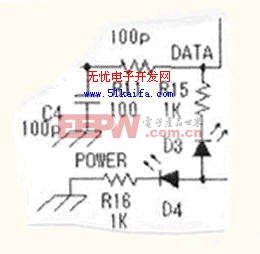

圖5LED表示電路

3.LED表示電路

在CPLD編程寫入器電路設計中還設計有各種LED表示電路。如設置有綠色LED來表示電源輸出情況,紅色LED在TDI信號為L低電平時點燈。在紅色LED點滅時表示傳送數據中,此時不能關機或拔連接電纜。LED表示電路如圖5所示。

4.Device切換電路

對不同的CPLD芯片(如PC84,PC44等)進行編程寫入,它的選擇由旋轉切換開關來完成,由于篇幅的關系就不給出了。

基金資助:本文由江蘇省高校自然科學研究指導性計劃項目資助,編號:05KJD510122

本文作者創新點及其經濟效益:設計出CPLD脫機編程寫入器,對CPLD進行編程寫入,而不需要開發實物基板,實物基板設計時就不需要留有JTAG接口。這樣能節約基板,減少產品體積。

周杰導師評論:該同學在書寫這篇文章的過程中,閱讀大量有關書籍,通過對CPLD的發展、結構、應用和設計等方面的認知,了解CPLD的基本原理,并設計出了CPLD脫機編程寫入器的電路圖,有一定的創新思想和經濟價值。

參考文獻:

[1]付慧生.《復雜可編程邏輯器件與應用設計》.中國礦業大學出版社,2003.8.TP332.1

[2]王道憲.《CPLD/FPGA可編程邏輯器件應用與開發》.國防工業出版社,2004.1.TP332.1

[3]孫航.《Xilinx可編程邏輯器件的高級應用與設計技巧》.電子工業出版社,2004.8.TP332.1

[4]趙妍肖冬榮.《幾種網絡控制系統的比較及典型應用》.微計算機信息.2006.(4-1):P40-42.

評論