低電壓PLD/FPGA的供電設計

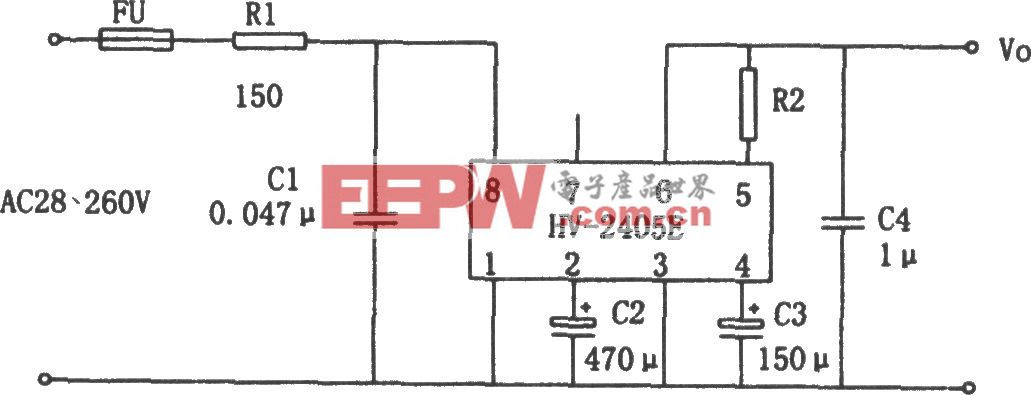

圖:AS28151.5A低壓差線性穩壓器應用電路,左邊為輸出可調型,右邊為3.3v固定輸出型

那么如何得到3.3v,2.5v等低電壓呢?通常我們可以采用三種方法:

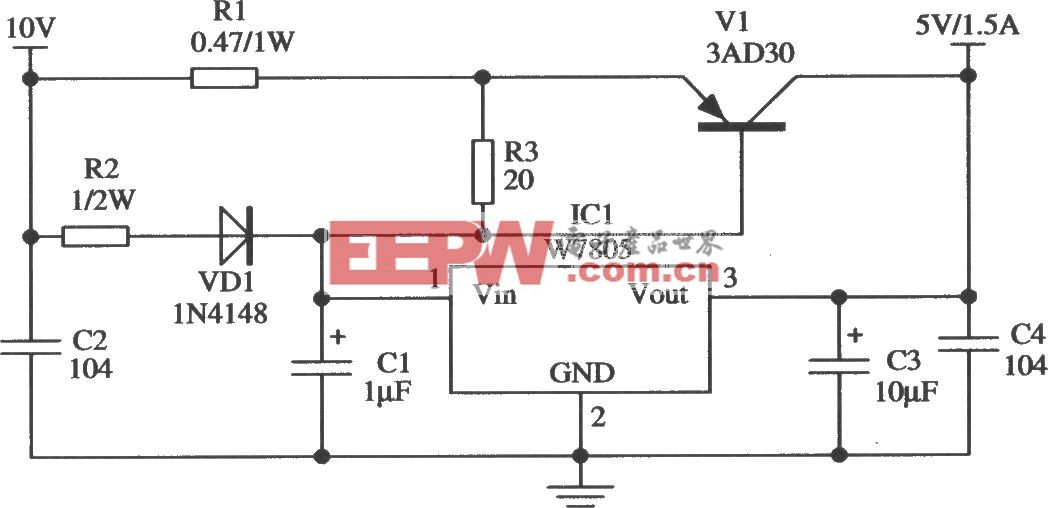

1.采用低壓差線形穩壓芯片(LDO)

線形穩壓芯片是一種最簡單的電源轉換芯片,基本上不要外圍元件。但是傳統的線形穩壓器,如78xx系列都要求輸入電壓要比輸出電壓高2v-3v以上,否則不能正常工作,但是5v到3.3v的電壓差只有1.7v,所以78xx系列已經不能夠滿足3.3v或2.5的電源設計要求。面對這類需求,許多電源芯片公司推出了LowDropoutRegulator,即:低壓差線形穩壓器,簡稱LDO。這種電源芯片的壓差只有1.3-0.2伏,可以實現5v轉3.3v/2.5v,3.3v轉2.5v/1.8v等要求。生產LDO的公司很多,常見的有:ALPHA,Linear(LT),Micrel,Nationalsemiconductor,TI等

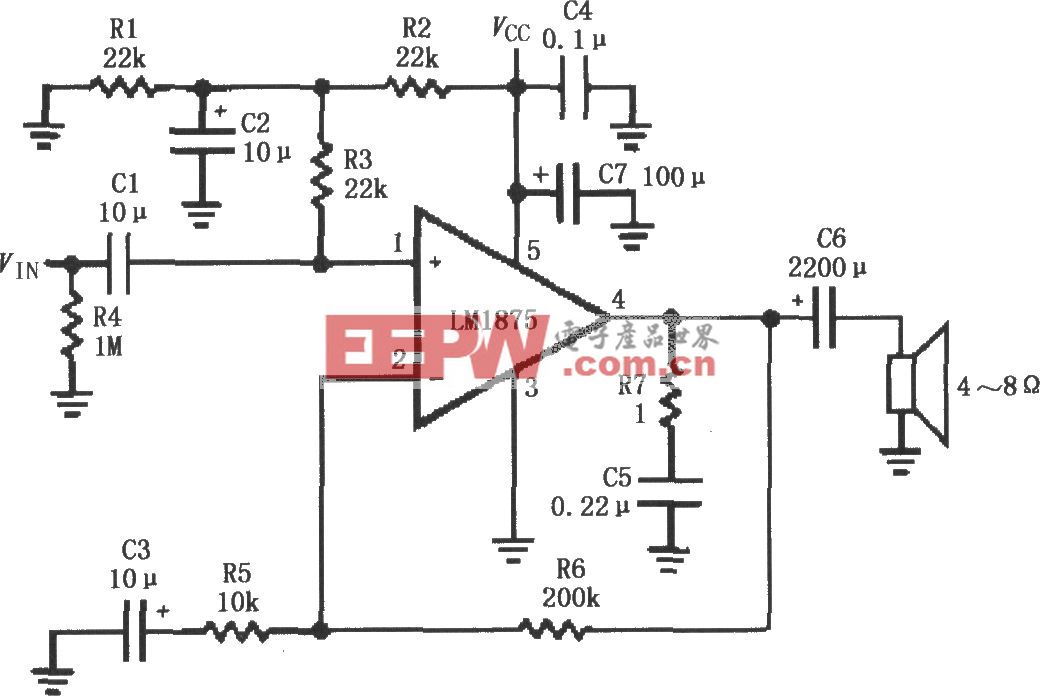

圖LT1530-3.35v轉3.3v/14A應用電路和效率圖

3. 直接采用電源模塊

考慮到開關電源設計的復雜性,一些公司推出了基于開關電源技術的低電壓輸出電源模塊,可靠性和效率都很高,電磁輻射小,而且可以許多模塊可以實現電源隔離。用戶只需要加很少的外圍元件即可使用。電源模塊最大的缺點是價格昂貴。 常見生產電源模塊的公司有:agere(原來朗訊的微電子部),Ericsson(愛立信),Vico(懷格)等等

三種電源方案的比較:

| 低壓差線性穩壓器 | 開關電源 | 電源模塊 | |

| 優點 | 所需外部元件數目少,使用方便,成本低,所需電路板空間小(不加散熱片時),紋波小,無電磁干擾 | 效率高(一般大于80%),輸入電壓范圍較寬,輸出功率大,價格比電源模塊便宜很多 | 效率高(一般大于85%),輸入電壓范圍較寬,輸出功率大,使用方便,電磁干擾小 |

| 缺點 | 效率很低(一般低于70%),功耗較大 | 設計較復雜,有電磁干擾,需要一定的設計能力 | 價格昂貴 |

最終應該采取何種電源設計方案,取決于我們設計的具體要求。通常小功率或對電源效率沒有要求的時候,可以采用LDO。 如對效率有較高要求,或電源功率較大,則應該使用電源模塊或自己設計開關電源,最終是采用電源模塊或自己設計開關電源,則取決于成本要求和自己的設計能力。

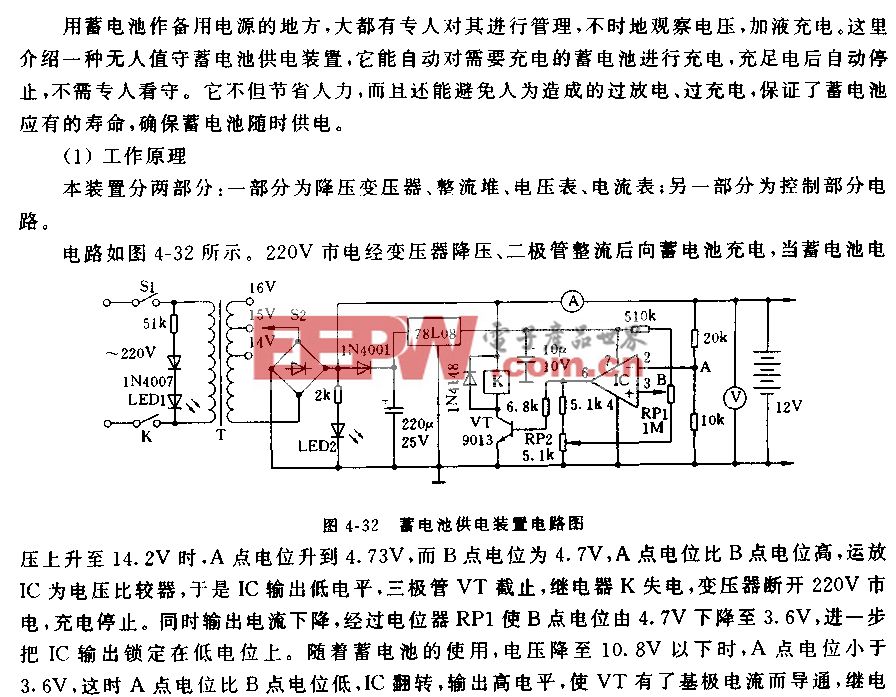

評論