量程自動轉換的12位十進制等精度數字頻率計

VHDL是一種快速設計電路工具,目前已成為IEEE的一種工業標準硬件描述語言。相比傳統電路系統設計方法,VHDL具有多層次描述系統硬件功能的能力,支持自頂向下(Top to Down)和基于庫(Library Based)的設計特點,因此設計者無需了解硬件結構,就可進行設計。

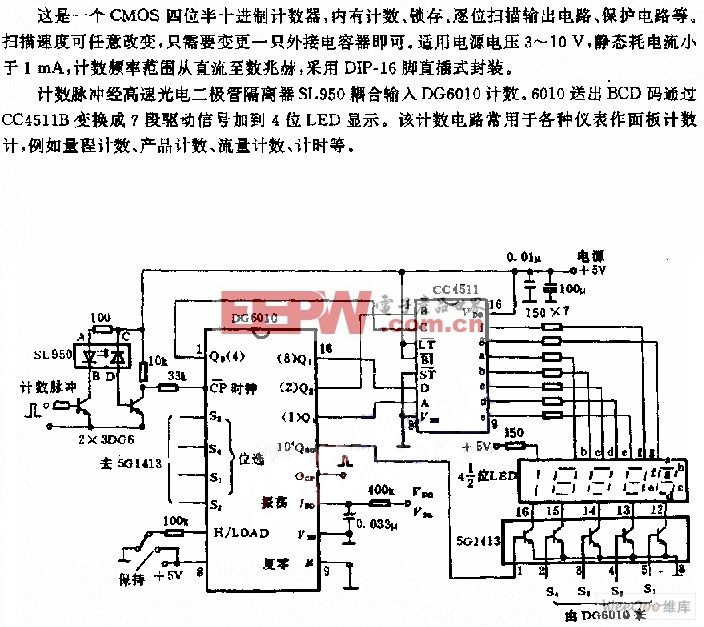

數字頻率計是數字電路中的一個典型應用,實際硬件設計采用的器件較多,連線復雜,而且會產生較大延時,造成測量誤差且可靠性差。隨著復雜可編程邏輯器件的廣泛應用,以EDA工具為開發手段,運用VHDL語言,從而大大簡化系統設計,提高整體的性能和可靠性。

2 數字頻率計測頻原理

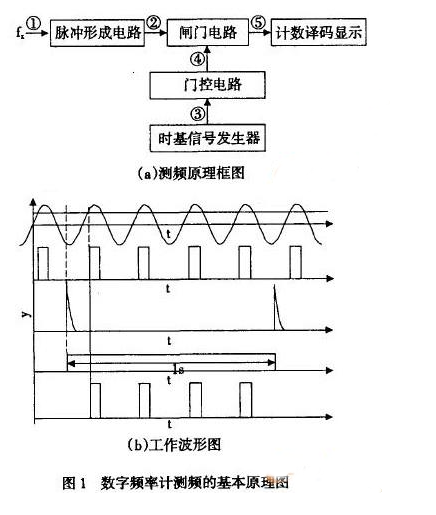

數字式頻率計的基本原理:使用一個頻率穩定度高的頻率源作為基準時鐘,來對比測量其他信號的頻率。通常情況下計算單位時間內待測信號的脈沖個數。單位時間可設置為大于或小于一秒。閘門時間越長,頻率值越準確,但閘門時間越長,每次測量頻率的間隔也就越長。閘門時間越短,測量的頻率值刷新越快,但將影響到測量的頻率精度。每次測量時,采用時基信號產生的閘門信號啟動計數器來對輸入的脈沖信號計數:閘門信號結束則將計數結果送入鎖存器,然后計數器清零,準備下次計數。如被測波形不好,可通過施密特電路整形。

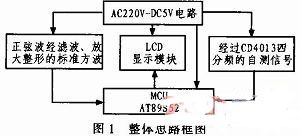

3 系統結構設計

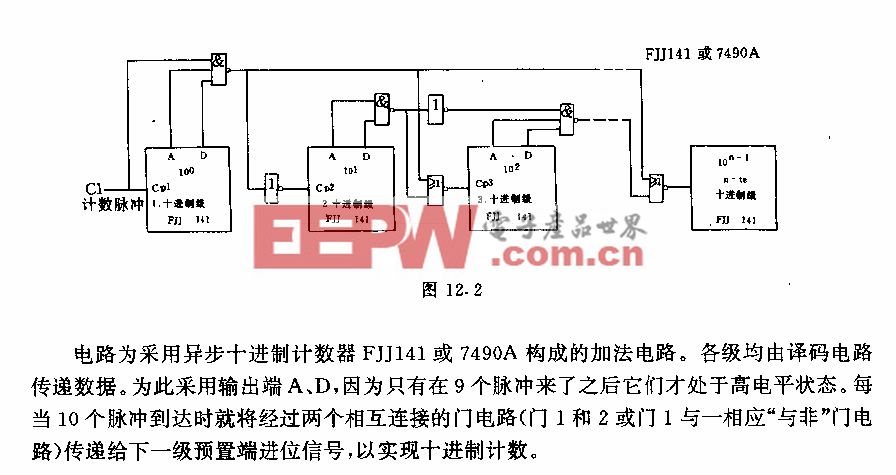

按照系統功能,數字頻率計系統分為二分頻、測量/校驗選擇、計數器、送存選擇報警電路、鎖存器、掃描顯示等模塊,如圖1所示。1 Hz時鐘信號作為測頻電路的輸入參考信號,經二分頻電路分頻后與測量/校驗選擇電路輸出的待測信號相比較,通過計數器電路在單位時間內計數脈沖數,時鐘下降沿結束計數:并將計數結果送至送存選擇報警電路,由送存選擇報警電路判斷,并完成對量程的選擇。若超限,則發出報警信號:最后再由鎖存器和顯示電路完成數據顯示。該系統整體設計的電路圖如圖2所示。

3.1 測量/校驗選擇模塊

測量/校驗選擇模塊采用二選一的選擇器實現。測量與校驗共用一電路,只是輸出信號CP1不同。其中各輸入信號:選擇信號sel、被測信號meas、測試信號test,而輸出信號為CP1。當sel=0時,為測量狀態,CPl=meas;當sel=1時,為校驗狀態,CPl=test。其仿真結果如圖3所示。

3.2 測頻控制信號發生器

測頻控制信號發生器采用分頻電路實現,采用1 Hz時鐘信號作為輸入信號。測頻控制信號發生器決定系統精度。本系統設計采用的二分頻電路,輸出占空比為50%,周期為2 s的方波。其仿真結果如圖4所示。相關設計程序代碼如下:

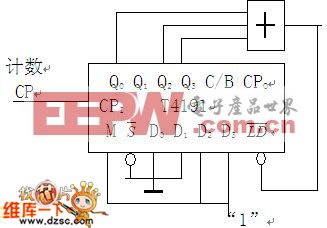

3.3 計數器模塊

計數器模塊對測頻控制信號發生器的輸出信號CP1進行計數,1 s定時后,將計數器中的結果送入鎖存器鎖存,同時對計數器清零,為下一次采樣測量做好準備,通過對十進制計數器例化實現。輸入信號:RD和CP用于計數開始、清零、鎖存;輸出信號為Q4~Q1。圖5所示為計數器模塊的仿真結果。其相關程序代碼如下:

3.4 送存選擇報警模塊

送存選擇報警模塊是本系統設計的關鍵,該模塊提供兩個功能:根據被測信號選擇量程,若超出量程則報警,鎖存數據。仿真結果如圖6所示。

設置超出量程檔測量范圍示警信號alert。

(1)若被測信號頻率值小于1 kHz(K=0)

計數器只進行三位十進制計數,最大顯示值為999 Hz:數碼管顯示被測信號頻率值,1 Hz~999 Hz量程檔,Y顯示綠色;如果被測信號頻率值超出該范圍,告警信號驅動燈光、揚聲器報警;

(2)若被測信號頻率值為1 kHz~10 kHz(K=1)

計數器進行四位十進制計數,取高3位顯示,最大顯示值為9.99 kHz,被測信號頻率值為數碼管顯示數值的1 000倍,1 kHz~10 kHz量程檔,Y顯示紅色。如果被測信號頻率值超出該范圍,則揚聲器報警。并給出相關程序代碼:

![]()

3.5 掃描顯示模塊

系統的掃描顯示模塊分為分時總線切換和顯示譯碼電路。分時總線切換用于顯示位的選擇,顯示譯碼用于顯示段的選擇。采用動態掃描顯示可使端口數目達到最少。

3.6 頂層設計

在頂層設計中對各模塊進行例化,實現整個系統設計。

4 結束語

通過對仿真結果的分析,系統設計達到了最初的設計要求,并使用康芯公司GW48EDA PK2/CK試驗系統對系統設計軟件程序進行驗證,同樣達到了設計要求。

評論