基于FPGA的RCN226絕對式編碼器通信接口設計

DSP在每個電流環周期發送一個有效的begin信號,20μs之后,碼盤信號接收模塊將接收到的數據存入FPGA內部雙口RAM的A口中,并按順序排列成16位數據的形式,然后向DSP發送end信號,表示一次通信結束,DSP接收到中斷之后從FPGA的雙口RAM的B口中讀取數據,完成一次通信, DSP的連接如圖3所示。本文引用地址:http://www.j9360.com/article/191929.htm

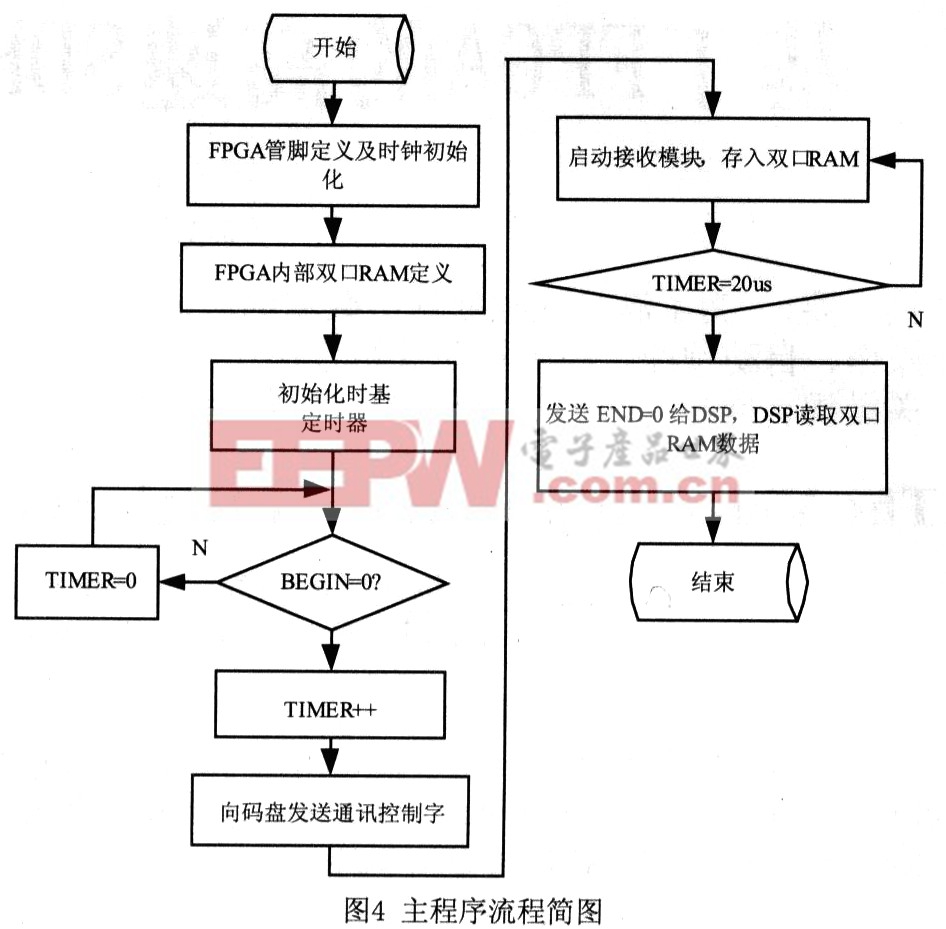

在本接口的研發過程中,對FPGA的開發采用Altera公司的Quartus II 5.1集成環境,硬件描述語言為VHDL語言。圖4為主程序流程圖。

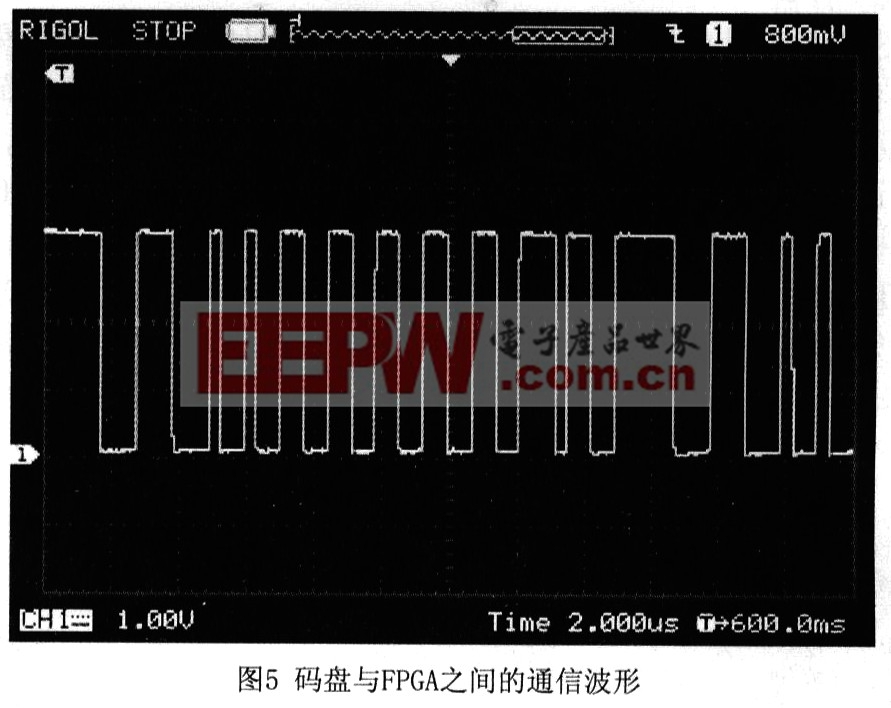

圖5為碼盤與FPGA之間的通信波形,從位置信號可以看出該接口工作正常。 |

3 結束語 |

fpga相關文章:fpga是什么

伺服電機相關文章:伺服電機工作原理

評論