直擴OQPSK系統載波跟蹤的 設計及FPGA實現

系統仿真時,可取10個二進制雙極性碼為信碼,中頻取7.2 MHz,載波NCO相位累加器的位寬為18位,載波NCO的參考頻率為28.8 MHz。這樣,載波NCO的輸出頻率精度為28.8 MHz/218≈0.1 kHz 。然后由NCO頻率控制字公式k=f02N/fc,即可計算頻率控制字的輸入。

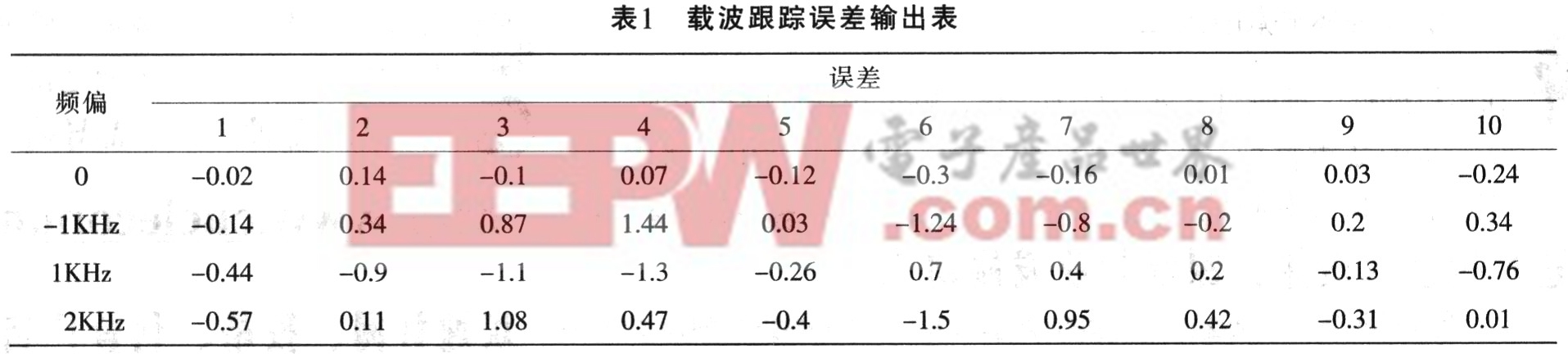

跟蹤環路中累加器的長度為一個信碼的長度即一個擴頻碼周期,由此發射載頻和本地載波跟蹤環路,即可輸出瞬時相位誤差,其具體數據如表1所列。本文引用地址:http://www.j9360.com/article/191856.htm

根據表1中的數據,由式ω=0θ/(NTpn)可計算出補償頻率,經驗證與頻偏大致相同(誤差不超過300 Hz)。其中θ為表1中的誤差,N為擴頻碼序列的長度;Tpn為擴頻碼一個碼片時間。把該補償頻率與載波NCO系統之前輸出的頻率相加,然后計算出載波NCO頻率控制字的輸入,即可產生所需頻率。在實際項目開發中,載波跟蹤環路算法可在FPGA中實現。

3 載波NCO的設計

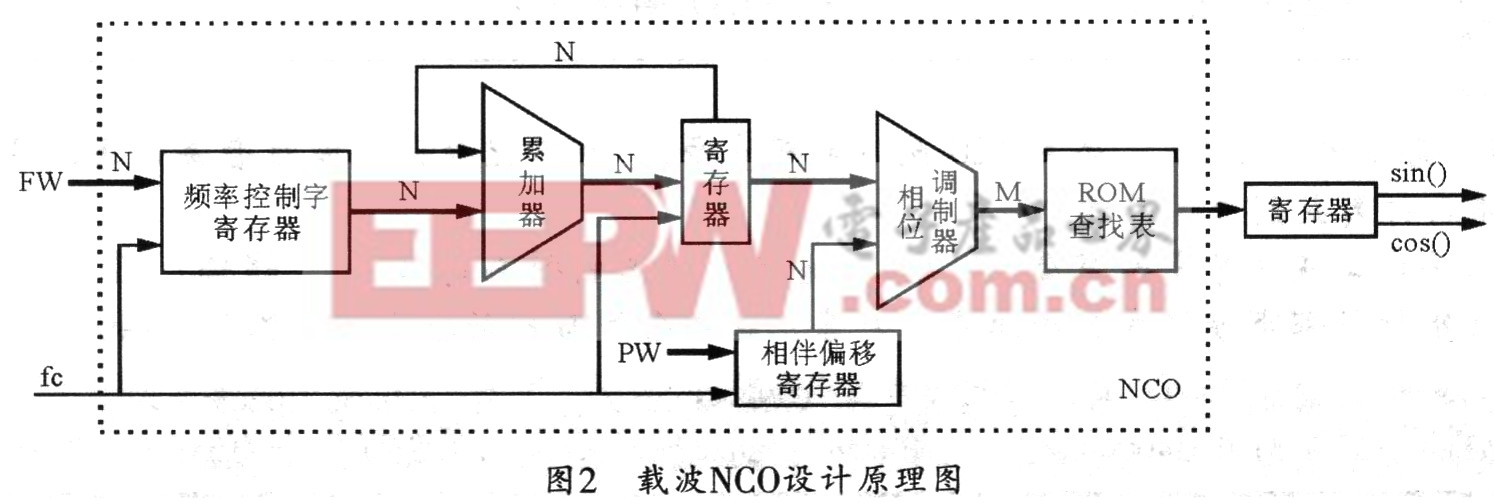

載波NCO可由ALTERA提供的IP核生成,也可由自己設計,圖2所示是載波NCO的設計原理圖。

由圖2可見,載波NCO主要由相位累加器、相位調制器和波形存儲器三部分組成。

3.1 相位累加器

相位累加器是NCO的核心,可完成相位累加功能。每來一個時鐘脈沖,累加器都將頻率控制字FW(N-1:0)與寄存器輸出的相位累加數據相加,再把相加后的結果送至累加器的輸入端。同時寄存器將加法器在上一個時鐘作用后產生的相位數據反饋到加法器的輸入端,以使加法器在下一個時鐘作用下繼續與頻率控制字進行相加。這樣,相位累加器即可在時鐘的作用下進行相位累加。每當累加器加滿時,產生一次溢出,以控制各寄存器異步清零,從而完成一個周期動作。而當下一時鐘來時,再開始下一周期的累加。這里的頻率控制字與輸出頻率f0的關系式為:

k=f02N/f

3.2 相位調制器

相位調制器可接收相位累加器的相位輸出。這里應加一個相位偏移值,主要用于實現信號的相位調制,如PSK(相移鍵控)等,在不使用時可以去掉該部分,或加一個固定的相位控制字。

3.3 波形存儲器

波形存儲器即正弦ROM查找表,它采用相位累加器輸出的數據作為波形存儲器的取樣地址,然后進行波形的相位一幅值轉換,從而在給定的時間上確定輸出的波形的抽樣幅值。N位的尋址ROM相當于把0~360°的正弦信號離散成具有2N個采樣值的序列。若波形有D位數據位,則2N個采樣值的幅值將以D位二進制數固化在ROM中,這樣,按照地址的不同,就可以輸出相應的正弦信號的幅值。

4 結束語

本文介紹了直擴OQPSK系統載波跟蹤的原理及FPGA實現方法。經實際的系統調試證明,該方法能有效的抑制OQPSK調制的倒相現象,即能在相位誤差積累到一定程度后,有效地反饋到載波NCO的輸入端.從而有效實現對高速運動目標的載波跟蹤。

評論