基于FPGA的語音信號LPC參數提取算法的實現

2.3 舒爾遞推模塊

舒爾遞推算法一個很重要的特點是在整個遞推過程中全部參與運算的量的初值、中間值和最終值皆小于1,因此特別適宜于采用定點運算的硬件系統來實現。該模塊的設計也采用雙RAM結構和同時取數同時運算的并行處理技術,所有運算單元的精度都是16位,每處理一次遞推過程,就輸出一個K(m)值。

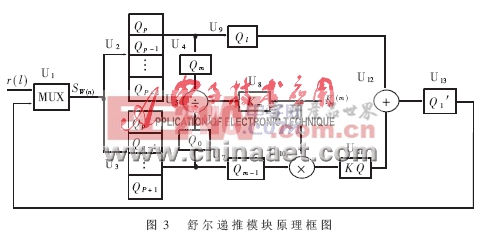

舒爾遞推模塊的原理框圖如圖3所示。圖中U2、U3為12×16bit的雙口RAM;U4、U6、U7、U8、U9、U11、U13為數據寄存器;U5、U10、U12分別為16位的除法器、乘法器和加法器;U1為多路轉換開關。該模塊的工作過程是:當歸一化自關函數r(l)通過U1送入U2和U3后,立即從中取出Qm和Q0送入除法器U5進行除運算,除得的結果送入U8;與此同時又分別從U2和U3中同時取出Ql和Qm-l,將Qm-l與Km在U10相乘后,送入U11,接著與Ql在U12進行相加,將結果經U13、U1重新送回U2和U3,接著又進行下一輪遞推,該過程一直要進行到遞推階數完成。在每一次遞推過程中,當U12在進行當前數據的加運算時,U10就可進行下一個數據的乘運算。這樣整個過程就可在連續的流水線方式不間斷地進行。

2.4 算術運算單元

本系統所用到的算術運算單元有加法器、乘法器和除法器三種。加法器采用標準的全加器來構成,而乘法器則采用2的補碼的BOOTH乘法器。下面介紹除法器的設計思想和工作原理。

由于本系統所使用的除法運算都是商小于1的除法,而且除法運算又比乘法運算少得多,因此對速度的影響也較小。綜合考慮速度和資源占用兩方面因素后,設計了下面的算法來實現除法器。設有兩個數A和B,A是被除數,B是除數,現在求它們的商Q=A/B,Q1。現將Q表示成下列形式:

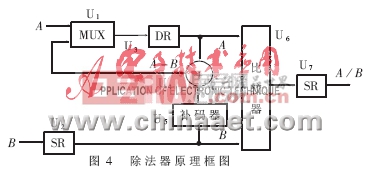

由于上述算法只需進行減法運算和除2運算,所以非常便于用硬件實現,據此算法設計的除法器原理框圖如圖4所示。圖中U2為并入并出移位寄存器,每右移一位,實現一次除2操作;U5為補碼器,它由反相器和加一電路構成,用于對B求補碼;U7為串入并出移位寄存器;U6為比較器,用于對A、B兩輸入數進行比較,若A≥B,則輸出“1”,否則輸出“0”;U3為數據寄存器;U1為多路轉換器;U4為加法器。該電路按下述原理工作:被除數A經U1送入U3并加到比較器U6的A端,除數B送入U2后右移一位再加到U6的B端。經U6比較后,若輸出“1”,則先將U6的輸出移入移位寄存器U7,再將A與B送入由U4和U5組成的減法器進行減法運算,所得差值再經U1送入U3;若輸出為“0”,則僅將U6的輸出移入U7即可。該步完成后,又將U2右移一位,再重復上述過程。整個操作一共要進行K次,最后U7中的數即為A/B的商。

在本系統中,將LPC分析與FPGA技術結合,充分利用了FPGA作為一種快速、高效的硬件平臺在數字信號處理領域所具有的獨特優勢,實現了語音信號特征參數的快速提取,為語音信號的進一步處理打下基礎。本系統采用50MHz的時鐘頻率進行工作。為考察其工作性能,對其整體性能指標進行了評估。由于影響整個系統速度的是乘法累加運算,因此它的工作性能也就決定了系統的性能。在求歸一化自關函數r(l)過程中,涉及到近200次的乘積累加,采用并行處理技術和流水線操作方式的FPGA則可以用接近50MHz的數據速率進行工作,整個系統的性能同其他芯片相比約提高40%~60%,因此用FPGA技術來處理語音信號具有得天獨厚的優點。

本系統除具有處理速度快的特點外,還具有獨立靈活的輸入輸出接口及一組檢測和控制信號線,可以方便地同任何一種處理器直接連接。由于FPGA自身所具有的抗干擾能力強、可靠性高的優點,本系統可廣泛應用于自動控制、工業機器人、語音合成和語音編譯碼等領域,特別對嵌入式系統的設計具有重要意義。

評論