基于FPGA的數字脈沖壓縮系統實現

2.2.3 塊浮點數據格式

在數字信號處理系統中,數據表示格式可分為定點制、浮點制和塊浮點制,它們在實現時對系統資源的要求不同,工作速度也不同,有著不同的適用范圍。定點表示法使用最多,簡單且速度快,但動態范圍有限,需要用合適的溢出控制規則(如定比例法)適當壓縮輸入信號的動態范圍,但這樣會降低輸出信號的信噪比。浮點表示法的優點是動態范圍大,可避免溢出,能在很大的動態范圍內達到很高的信噪比,主要缺點是系統實現復雜,硬件需求量大,成本和功耗高,而且速度較慢。

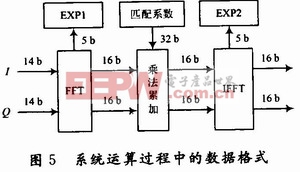

塊浮點表示法兼有定點法和浮點法的某些優點,是以上2種表示法的結合。這種表示法首先對一組數據進行檢測,歸一化最大數的小數部分,再建立適當的指數。接著把剩下數據的小數部分轉化為合適的數,使它們可以使用最大數的指數。塊浮點算法的主要優點是:大動態范圍、低截斷(或舍入)噪聲,是一種有效的數據表示形式。從芯片實現角度上看,塊浮點表示法能夠保證較高的信號處理質量,尤其適用于FFT運算的場合。脈壓模塊中的FFT核帶有塊浮點運算的功能,整個運算過程中的數據格式表示如圖5所示。本文引用地址:http://www.j9360.com/article/191544.htm

ADC輸入數據為14 b的二進制補碼形式,對其低位補零擴展為16 b(IP核要求的輸入精度)后送入FFT運算單元,輸出結果為16 b的定點數以及指數EXP1。復乘包括乘法和累加運算,即FFT結果與匹配系數進行16 b×16 b的乘法運算,所得結果再進行加法運算;在進行加法運算前,所有數據擴展為33 b以防止溢出的發生,最終數據截取高16 b送入IFFT處理單元,輸出為16 b的定點數和指數EXP2,將其與EXPl相加后

得到指數EXP。脈壓的最終結果即為IFFT后的16 b定點數以及指數EXP,兩者分別存儲在FPGA片內RAM中。

2.3 脈沖壓縮模塊的測試

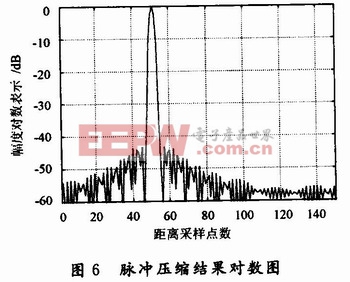

設輸入理想LFM信號參數如下:帶寬B=40 MHz;時寬T=6μs;系統樣本速率為60 MHz;使用海明窗加權。在上述條件下,脈沖壓縮系統的輸出結果對數圖如圖6所示。

在圖6中,橫軸代表距離采樣單元,即系統最小距離分辨率。通過系統實際處理結果與Madab仿真結果的對比驗證了設計的正確性和實用性。

3 結語

系統采用ADS5500完成14位、60 MSPS的數據采集,并在FPGA中實現1 024點的數字脈沖壓縮。設計采用并行流水方式提高工作速度,而塊浮點算法則充分保證運算的精度。IP核的復用大大降低硬件規模,從而使整個系統具有高速度、高精度和低功耗的特點。

評論