基于FPGA的大動態數控AGC系統設計

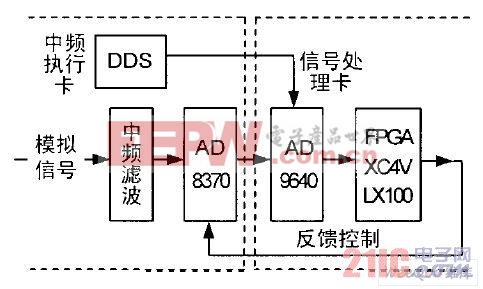

3 硬件實現

硬件方案的具體實現如圖3 所示。上面為信號處理板卡,下面為中頻執行板卡。其中控制板卡上AD 轉換由AD9640 芯片完成,輸入信號的峰峰值可設置范圍為1~ 2 V,本系統初始化為2 V; 控制部分在FPGA XC4VLX100 中完成,以產生時鐘、使能和數據三線控制信號; 作為環路執行元件的是前端中頻板上的AD8370,其控制功率增益范圍為- 11~ + 34 dB; 3 dB帶寬為750 MHz; 串行的8 bit 控制信號接口; 提供200Ω差分輸入和100Ω差分輸出。由于本方案動態范圍需達60 dB,故采用了2 級AD8370 級聯,為了讓系統工作穩定,設計時應使2 級的放大倍數盡量接近,以避免第2 級出現飽和,因此在將調整的倍數轉化為AD8370 控制字時,需特別注意。

圖3 硬件測試板卡

系統由微波信號源4438C 產生中頻70 MHz、比特率4 Mbps 的QPSK 信號,采樣時鐘64 MHz,由前端中頻部分的DDS 產生,系統抽取率仍為8,由DDC后的CIC 完成。

實現中,I、Q 兩路的均方值由FPGA 中乘法器DSP48 求取,累加器完成均方值的累加,而累加樣本點的個數直接決定了控制調整的相應速度,累加長度太長會使相應速度變慢,無法跟上信號的變化; 但長度太短又會使估計的功率值不準,起伏太大從而引起控制精度的下降,通過實測發現通常數百符號即可得出較準確的信號功率估值,因此對符號率百K 以上量級的信號而言可以在數毫秒甚至更短的時間內完成信號的精確調整。本系統設置為1 ms 進行一次調整,即2 048 個符號得到一次估計值。此外,求對數運算以及信號需調整的倍數到控制字的轉換都通過查表實現,其中增益控制字查找表的可實現增益為- 13~ + 60 dB,其深度為4 096,即每1 dB的變化對應56 個步進,可實現最小0. 02 dB的調整,因此結合之前的準確估計一起實現了較高的控制精度。

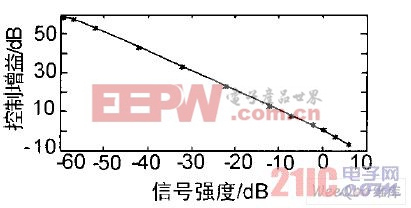

為避免低信噪比情況下AD 長時間工作在溢出狀態,系統設置的參考值設計為比AD 滿量程小2 dB左右。經測試,當4 dBm 的QPSK 信號直接輸入AD 時,AD 采集信號的量化值為# 6 000 左右,距14位滿量程對應的# 8 192 約2 dB,故以此功率為參考。如圖4 所示,橫軸為輸入信號功率,縱軸為AGC的增益。理論上2 級AD8370 級聯能實現90 dB 的動態,但實測中,在信噪比10 dB 條件下,單級在- 7~ + 28 dB 范圍,2 級聯合在- 14~ + 56 dB時,其線性性較好,故在本系統中實現了近70 dB的動態范圍。

圖4 輸入信號強度及對應的AGC 增益

4 結束語

首先介紹了數控AGC 的原理,指出AGC 的數字實現方法的優點。在此基礎上,對功率檢測以及反饋控制方法進行了計算機仿真,結果表明,該方法是可行的,適合FPGA 實現。在硬件實現中,通過2級AD8370 級聯實現了近70 dB 的動態范圍變化,并保證了控制精度誤差小于1 dB。

評論