高精度DDFS信號源FPGA實現

1)相位累加器(地址發生單元) 設計思路為根據輸入的Step值,計算出1/4周期采樣的點數m,然后在時鐘作用下進行計數,當計數值達m個時,說明一個象限內已經取完點,此時象限控制字自加1,計數變量重新置零,此時依次產生了如下(0,Step,…,(m-1)Step)的30位二進制地址。截取此地址位的高10位即可用于對ROM空間的尋址。根據正弦信號的特點,下一象限產生的地址應該為:((m-1)Step,(m-2)Ste-p,…,0),依此類推。且象限控制字自加。

2)ROM存儲單元 ROM存儲單元的數據可以通過Matlab進行計算獲得,并將其存儲為dds_sin.mif。也可采用其他高級語言來獲得ROM存儲數據。

3)補碼轉換電路 (0,π)數據直接輸出,(π,2π)象限的數據應進補碼運算。對此補碼電路稍作修改,即可同時輸出相位正好相反的兩路正弦信號。

4)數據延時單元 為了使地址單元輸出的象限控制字等與異步ROM配合工作,應對相應的數據進行延時,以保證輸出數據的正確。本設計中對相位控制字延了一個時鐘周期。

3 DDFS設計模塊性能及所占資源分析

1)DDFS模塊時序分析 首先應當分析DDFS模塊的最大時鐘頻率fmax,因為它決定著系統能否工作在150 MHz或更高的時鐘頻率。通過Qu-artusII6.0自帶的Timing Analyzer Tools時序分析,本設計中的DDFS模塊的fmax=179.18 MHz,高于150 MHz。故本設計理論上可輸出的正弦信號的最高頻率可達11.198 MHz。

2)DDFS模塊資源分析 本設計使用的是FPGA為Ahem公司的CycloneⅡ系列芯片EP2C5Q208C8,所設計的DDFS模塊所占片上資源邏輯單元僅為2%,所占的數據存儲空間為12 288 bits,約占總的數據存儲空間119 808 bits的10%。可見,通過對ROM存儲表進行數據后,DDFS模塊所占片存儲資源較少。因此,FPGA上ROM資源允許調用若干DDFS模塊來完成各種功能模塊,如2-PSK、2-FSK、2-ASK等數字調制。

4 系統性能仿真與測試

以DDFS模塊為基礎,本設計實現了兩組反相的正弦信號、余弦信號、三角波信號、鋸齒波、2-PSK、2-FSK、2-ASK等數字調制信號、掃頻及任意次波形輸出等功能。

在本設計中,仿真主要通過QuartusII6.0自帶的Simulator Tool來進行數據仿真。從仿真圖上可驗證該設計的正確性。同時,通過Qu-artusII6.0自帶的Signal TapⅡ邏輯分析儀來進行邏輯功能的硬件驗證。

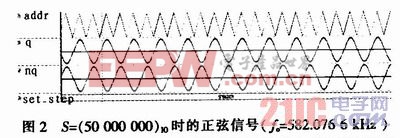

1)基本正弦信號輸出 在本設計中同時產生兩組信號,一組為正弦信號,另一組與之反相。圖2是步進長度設定為(50 000 000)10時的正弦信號Signal Tap II采樣圖,其頻率分別為fo=582.076 6 kHz。此時輸出信號為可產生的最高頻率。從所獲得的輸出信號的波形上看,頻率較低時,曲線穩定且光滑;頻率較高時,波形失真也并不大,可以通過后級濾波網絡進行波形的進一步平滑。且頻率穩定度相當高。本文引用地址:http://www.j9360.com/article/191312.htm

在外部時鐘50 MHz的頻率下,可以獲得的最高頻率約為3.125 MHz,最低頻率及頻率步進可以低至11.64 MHz。當對外部時鐘信號倍頻至150 MHz后,最高輸出頻率可以達到9.375 MHz,最低頻率及頻率步進可以低至34.925 MHz。進一步提高頻率及模塊性能,能獲得更大頻率范圍的信號。

評論