基于FPGA的多路圖像采集系統的軟件設計

3 ITU656解碼

ITU656解碼模塊根據ITU656標準將4:2:2的數據流解碼成ITU656標準視頻流。ITU656并行接口除了傳輸4:2:2的YCbCr視頻流外,還有行、場同步所用的控制信號。PAL制式的圖像一幀有625行,每秒掃描25幀;每行數據由1128字節的數據塊組成。其中,PAL制式23~311行是偶數場視頻數據,312~552行是奇數場視頻數據,其余為垂直控制信號。

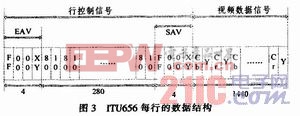

圖3為ITU656每行的數據結構。每行數據包含水平控制信號和YCbCr視頻數據信號。視頻數據字是以27兆字/秒的速率傳送的,其順序是:Cb,Y,Cr,Y,Cb,Y,Cr,…其中,Cb,Y.Cr這3個字指的是同址的亮度和色差信號取樣,后面的Y字對應于下一個亮度取樣。每行開始的288字節為行控制信號,開始的4字節為EAV信號(有效視頻結束),緊接著280個固定填充數據,最后是4字節的SAV信號(有效視頻起始)。本文引用地址:http://www.j9360.com/article/191256.htm

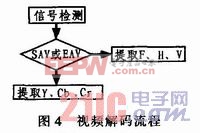

SAV和EAV信號有3字節的前導:FF、FF、00;最后1字節XY表示該行位于整個數據幀的位置及如何區分SAV、EAV。在每個時鐘的上升沿讀取從解碼芯片傳來的8位數據。當檢測到一行數據的開始標志FF0000XY時,檢測到SAV信號或EAV信號,提取H、F、V信號。然后發出開始命令,同時開啟行列計數器,開始對接下來的圖像數據進行解碼,根據每個8位數據自身帶的信息,判斷該數據為Y,Cr還是Cb,從而得到Y,Cr,Cb各分量的值。解碼流程如圖4所示。

4 幀存儲控制器與LCD/VGA顯示控制器的設計

4.1 數據格式的轉換

根據前面第2節的介紹,從ITU656解碼模塊出來的數據為8位4:2:2的YUV空間圖像數據,而LCD/VGA顯示器只能接收RGB數據。因為Y-CrCb4:2:2格式不能直接轉換為RGB,所以需要先轉換為YCrCb4:4:4格式。

我們知道解碼芯片得到的視頻數據是順序為Cb,Y,Cr,Y,Cb,Y,Cr,……的序列,存儲的時候將一個Y與一個C(Cb或Cr)結合起來組成一個16位的數據。而當數據被讀出來時就要將這些視頻數據轉換為每個像素占24位(Y、Cb、Cr各占8位)的4:4:4的數據流。4:2:2到4:4:4的轉換采用最簡單的插值算法,在采樣的時候,每隔一個像素才采一次色度值(Cb和Cr)。在轉化時,直接將前一個有色度信息的像素點

的Cr以及Cb的值直接賦給后一個像素的Cr和Cb,這樣就能得到4:4:4的像素數據,每個像素占用24位位寬。

4.2 幀存儲控制器

作為系統的重要組成部分,幀存儲控制器主要用來進行有效數據的緩存。視頻數據在FPGA1的控制下乒乓寫入兩片SRAM。乒乓技術應用的關鍵在于乒乓切換信號frame的產生,本系統中根據視頻解碼芯片的奇偶場信號RTS0來產生幀切換frame信號,也就是一個RTS0周期切換一次。一個RTS0周期由一個奇場和一個偶場組成,是一副完整的畫面。當frame為1是,FPGA通過計數器的計數截取最終顯示所需要的有效的像素點信息按照SRAM的控制時序寫入SRAM1,同樣當frame為0時,將對應的像素信息寫入SRAM2,如圖5所示。

系統加電的同時,4片視頻解碼芯片同時工作,為了保證數據采集的準確性和顯示的同步性,系統內生成一個八倍于像素時鐘的寫時鐘信號write_clk,這樣,在一個像素時鐘周期,寫時鐘信號已經過了八個周期,而每兩個周期分別完成一路圖像數據的寫過程。

由于SRAM是一維存儲空間,一個地址對應一個數據。所以在寫入數據時將SRAM的地址空間劃分為4段,每一段用來存儲一路圖像數據。

評論