增量設計流程針對需要變更部分進行優化

本文引用地址:http://www.j9360.com/article/191195.htm

步驟四:在物理實現環節將更新的網表導入Libero

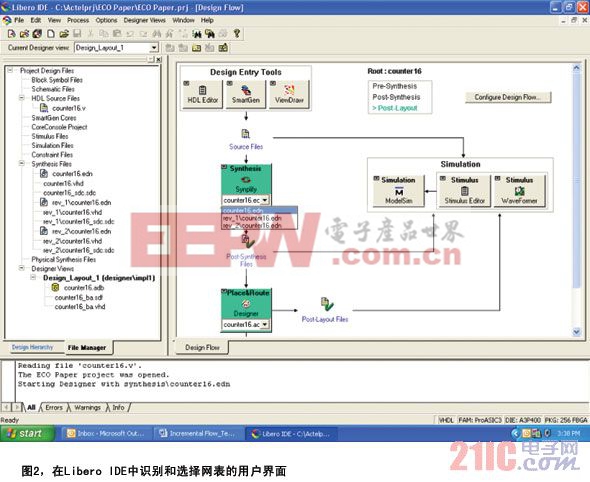

一旦Synplify Pro生成網表,就自動成為Libero IDE文檔管理器的一部分,并且可用于布局布線 (即可被布局功能調用)。在設計流程和文檔管理器與Libero之間的用戶界面上,你很容易就找到和選出Synplify Pro創建的網表實現方案(參見圖2)。

假設該網表是更新后的網表,包含設計和綜合過程中產生的增量變更,你可能首先希望保護Libero的初始布局布線過程生成的原始布局。在Libero中,你可輕松地將原始布局保存為物理設計“View”(也叫做“implementation”) 文件,可按使用方便給該視圖命名,比如命名為“Design_Layout_1”。Libero不會用更新的網表結果覆蓋“Design_Layout_1”這個文件,它允許在同一項目中創建新的View。例如,可將名為“Design_Layout_2”的文件用于存放更新網表的實現和測試結果。這個功能使用戶能夠比較用Synplify Pro產生增量網表變化前后的結果。

接下來,在Libero中打開Actel的物理實現工具Designer,將更新的網表用新的實現方案名稱導入Libero,并編譯設計。編譯設計后,在Libero的布局選項中完成設計布局。該菜單的缺省選項會對整個布局進行重新布局布線。對于包含經MultiPoint更新后的網表,Actel建議采用完全布局布線。完全布局布線的布局效率最高,但需要對所有時序進行重新驗證。從增量修改策略的角度來看,只對那些直接受增量變化影響的布局部分進行重新布局布線也許更為有利。布局選項菜單包括“Place Incrementally”(放置增量)、“Lock Existing Placement (Fix)”[鎖定現有放置 (修正)]和“Route Incrementally”(布線增量)

評論