JPEG2000中5/3離散小波多層變換FPGA實現研究

二維小波變換結果就是,在行變換結束之后對于行方向上面的LH分量再做列方向上的小波變換,得到LL,HL,LH,HH分量,對于多層小波變換就是在前一層變換的結果上對LL子帶再進行二維DWT變換,多層小波變換的示意圖如圖6所示。

4.2 FPGA測試驗證

該設計的FPGA驗證采用Altera的DE2開發板平臺,開發板采用CycloneⅡEP2C35作為主FPGA芯片,具有豐富的I/O接口與顯示存儲設備,可以滿足該設計的驗證工作。

本次FPGA的驗證中使用Altera的SignalTapⅡ嵌入式邏輯分析儀。SignalTapⅡ嵌入式邏輯分析儀集成到QuartusⅡ設計軟件中,能夠捕獲和顯示設計中實時信號的狀態,這樣開發者就可以在整個設計過程中以系統級速度觀察硬件和軟件的交互作用。它支持多達1 024個通道,采樣深度達128 Kb,每個分析儀均有10級觸發輸入/輸出,使用SignalTapⅡ無需額外的邏輯分析設備,只需將一根JTAG接口的下載電纜連接到要調試的FPGA器件即可。

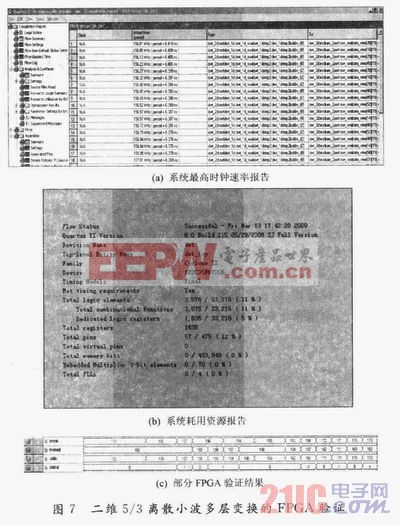

下載驗證結果如圖7所示,整個系統時鐘可以達到156 MHz,速度很快,耗用資源相對較少,運算結果正確。本文引用地址:http://www.j9360.com/article/191091.htm

5 結語

本文提出了一種快速、有效的JPEG 2000 5/3小波變換的VLSI設計結構,該結構將數據的奇偶分裂、邊界延拓嵌入到地址產生單元對雙端口RAM的操作中,不需要額外的計算單元,采用移位-相加操作代替卷積操作,通過Verilog編寫RTL級代碼并進行功能仿真,最后完成了在FPGA上的驗證,最高時鐘頻率達到156 MHz,整體性能優越。

評論