基于FPGA的可鍵盤控制計數電路的設計與實現

2.1.2 鍵盤掃描電路工作原理

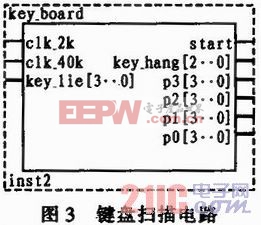

圖3為鍵盤掃描原理圖。CLK_40K為鍵盤掃描工作時鐘,連續讀取數據輸入端KEY_LIE[3..0]的信息;CLK_2K為鍵值控制工作時鐘信號,無鍵按下時控制電路循環掃描輸出;P3,P2,P1,P0為鍵盤譯碼輸出BCD碼形式;START端為數據輸出標志信號,當P3-P0輸出時,START端輸出一個脈沖。工作時,由行信號輸出端KEY_HANG[2..0]循環輸出“110”,“101”,“011”。當沒有按鍵按下時,掃描電路列信號輸入端檢測到“1111”。當有按鍵按下時,例如按下1鍵,此時行信號KEY_HANG[2..0]輸出“011”,由圖2可知。列信號輸入端將檢測到“0111”,在掃描譯碼時,可根據行信號輸出和列信號輸入數據同時判斷“0110111”對應數據為1。本文引用地址:http://www.j9360.com/article/190980.htm

2.1.3 鍵盤掃描電路VEIDL實現

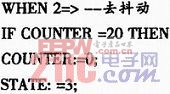

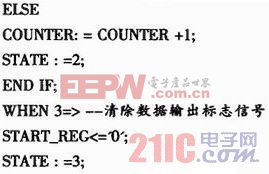

鍵盤掃描電路主要有判斷按鍵有無按下,鍵值識別和去抖動處理等功能。其中去抖處理主要為了避免外界振動引起按鍵誤動,以及保證按鍵每穩定閉合一次,系統僅對其響應一次。采用不同的鍵盤其機械抖動時間各異,本文設置去抖時間為20 ms。圖4為鍵盤掃描電路VHDL描述流程圖。以下是去抖動程序關鍵代碼:

2.2 可預置數BCD碼計數電路

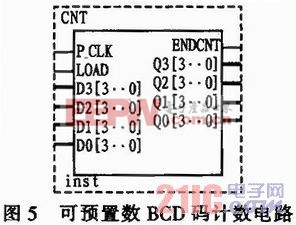

圖5為可預置數BCD碼計數電路。置數端LOAD為高電平時,將通過鍵盤設置的數并行置入到D3~D0。然后對輸入的脈沖直接進行BCD碼減法計數,由Q3~Q0輸出。計數結束,ENDCNT端輸出一個脈沖。

評論