基于FPGA的HDB3碼編碼器優化設計與分析

2.2 HDB3極性變換

在極性變換中,將使用四選一模擬開關實現+1,0,-1的波形輸出。實現真正意義的HDB3碼的輸出,這里選用的是數字芯片CD4052來實現。

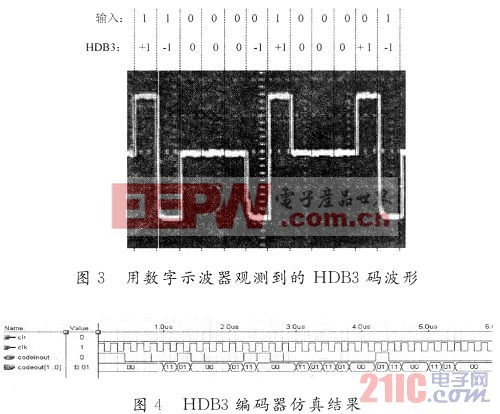

在單雙極性變換設計與實現部分,要實現將3位的編碼轉換為2位的編碼,也就是將前面的+1,-1,+V,-V,+B,-B,0轉換成用兩位來標識,這樣才能通過CD4052的兩個輸入端進行不同的組合,從而選通不同的通道,實現HDB3碼的+1,-1,0三種電平的輸出。而轉換的方法和編碼時確定的極性是一致的,分別用10,01,00來標識+1,-1,0。在數字示波器下觀測到的波形如圖3所示。本文引用地址:http://www.j9360.com/article/190568.htm

2.3 結構化HDB3碼編碼器設計

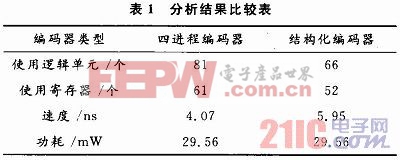

在該設計中,將使用元件例化語句來實現HDB3碼編碼器。底層文件主要分為序列發生器、插“V”模塊、插“B”模塊、單雙極性變換模塊,加上頂層文件共5個模塊。在該設計中,用11標識+1,01標識-1,用00標識0。其中codeinout是用來觀察序列發生器產生的二進制代碼序列,做為HDB3碼編碼器的輸入序列,codeout為HDB3碼的編碼輸出。該設計運用VHDL硬件描述語言的元件例化語句來實現HDB3碼編碼器的設計,共一個頂層文件和4個底層文件。在編碼中,選用2位二進制對HDB3碼編碼的插“V”和插“B”以及輸出進行編碼,且用的均為非歸零碼來表示。對元件例化語句二位編碼的設計進行波形仿真結果如圖4所示。

從圖4中可見,輸出的編碼序列和編碼規則一致,說明設計正確。

3 HDB3碼編碼在FPGA中實現的特性分析

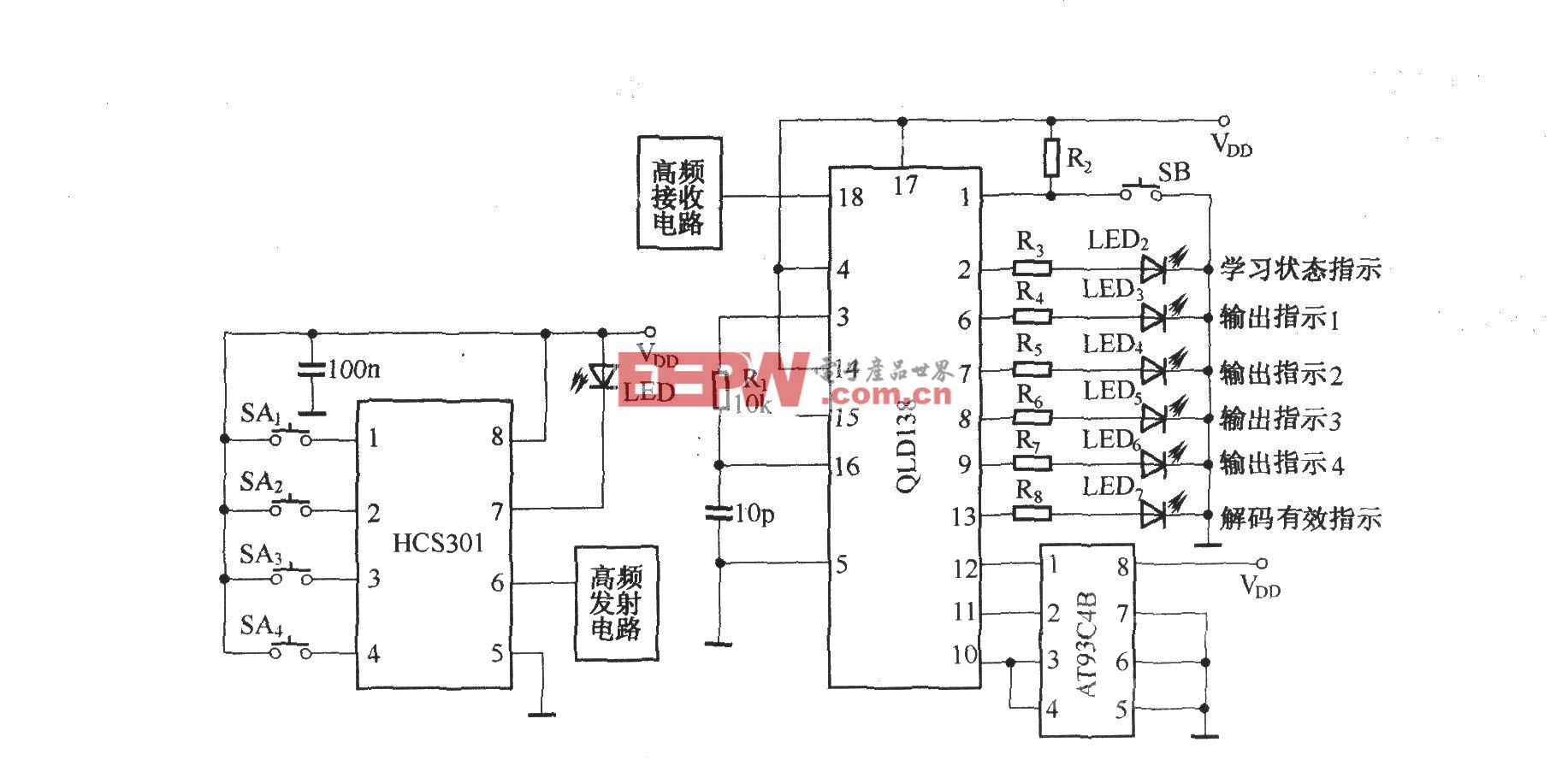

選用cycloneⅡ系列EP2C5T144C6器件,利用QuartusⅡ7.2對兩種不同設計的HDB3編碼器進行了分析。分析的主要內容包括:邏輯單元的占用、寄存器的占用、工作速度及功耗等的比較。仿真之后,主要選擇了兩組結果進行比較。分析結果如表1所示。從仿真結果可以看出,在結構化設計中,編碼器總邏輯元件、專用寄存器使用與四進程設計相比各減少了18.5%,14.8%,表明結構化設計有利于減少器件資源的使用。

4 結語

根據實驗和系統分析的結果,在FPGA中,利用VHDL語言設計HDB3編碼器是可行的。尤其是結合VHDL語言程序設計的特點,利用不同的設計方式,可實現對HDB3編碼器的優化設計。通過比較,在結構化設計中,編碼器總邏輯元件、專用寄存器使用與四進程設計相比各減少了18.5%,14.8%。因此,結構化設計有利于減少器件資源的使用。

評論