基于FPGA和FLASH ROM的圖像信號發生器設計

2 系統實現

2.1 USB接口模塊

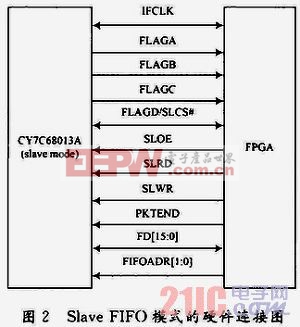

USB接口具有傳輸速度快、即插即用等優點,所以使用USB來實現PC機與系統的通信。CY7C68013A作為USB 2.0控制器,有3種接口工作模式:Ports,Slave FIFO和GPIF。根據系統構成和實際要求,選用Slave FIFO模式的數據傳輸方案。具體的硬件連接如圖2所示。本文引用地址:http://www.j9360.com/article/190175.htm

CY7C68013A通過固件編程來配置具體的功能。應用程序通過USB驅動程序建立與USB外部設備的聯系。本文采用了Cypress公司提供的通用驅動CyUsb.sys,該驅動程序完全滿足本系統設計的要求。應用程序可以通過兩種方式來訪問CyUsb.sys:

(1)使用Windows API如SetupDiXxxx和Deviceio Control;

(2)使用Cypress公司提供的CyAPI.lib。

本文采用CyAPI.lib來訪問USB驅動,CyAPI.lib提供了簡單高效的與Cyusb.sys通信的方法,方便掌握、可有效縮短USB設備的開發周期。

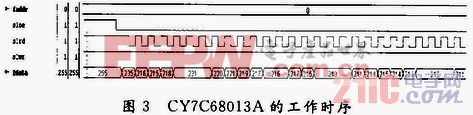

在完成圖像數據寫入功能時,FPGA接收到圖像數據寫入的命令后,使faddr地址指向用于下傳數據的端點FIFO,然后開始獲取來自USB控制器的數據,FPGA內部USB通信模塊工作情況如圖3所示。IFCLK是由FPGA提供的40MHz時鐘,CY7C68013A的端點FIFO被配置為同步工作。

評論