基于FPGA的高速多路視頻數據采集系統

SOPC系統以NiosII處理器為核心,通過AvaIon總線作為控制信號和數據傳輸中樞,NiosII軟核CPU及各類外設均掛載在Avalon總線上,本文SOPC系統中包括NiosII處理器、SSRAM、片上內存、JTAG控制接口、I2C總線控制接口、自定義FIFO接口、2個SDRAM控制器、DMA等。

2.2 視頻解碼模塊設計

視頻采集擴展板以TVP5150低功耗視頻A/D芯片為核心,采集模擬攝像頭信號,經A/D采樣后量化編碼成8位ITU-RBT.656視頻編碼格式輸出,輸出圖像分辨率為720x 480,像素時鐘為27 MHz。

視頻解碼模塊具有兩個功能:

①根據ITU-RBT.656并行接口規則,將TVP5150芯片輸出的數據流轉換成YUV422的圖像RAW DATA。

②對視頻分辨率進行調整,調整為640×480的分辨率,當數據為有效區域像素時發出數據有效信號,即對自定義FIFO的寫請求信號。

ITU-RBT.656協議中規定的信號中主要有3類:有效視頻區域數據信號、視頻定時基準信號、輔助信號。視頻解碼模塊第一部分任務關鍵是如何快速檢測ITU-RBT.656視頻數據流中視頻定時基準信號SAV/EAV。定時基準信號由4個字節的序列組成,其格式為FF0000XY,前3個字節FF0000為標志序列,最后一個字節XY表示該定時基準信號前后的數據行位于整個數據幀的位置及該定時基準信號類型。最后一字節XY每一位的含義如表1所列。本文引用地址:http://www.j9360.com/article/190015.htm

H,P2=FH,P1=FV,P0=FVH。

傳統序列檢測通常使用狀態機來實現。本設計創新的使用滑動窗法來快速檢測定時基準信號,這種設計程序結構清晰,在很大程度上減少了代碼量。根據ITU-RBT.656協議中定時基準信號的定義,聲明變量SAV=(Window==24’hFF0000)&(iData[4]==1’b0)。其中Window聲明24位寄存器,iData[7:0]是8位輸入信號,這里只取第4位。滑動窗更新時每次左移8位,低8位用輸入信號補齊。

解碼模塊的第二個功能在調整分辨率的時候引入Skip信號,當Skip信號有效時,該像素點數據跳過。本設計通過除法器控制Skip信號,將行像素計算器的輸出值作為除法器的分子,分母為9,skip信號由除法器余數控制,當余數為0時Skip信號有效。采用這種方案將行像素點由720轉換為640。

2.3 SOPC自定義FIFO接口

由于視頻輸入部分工作在27 MHz的時鐘頻率下,而NiosII軟核CPU為了獲取較高的系統處理能力,整個SOPC系統工作在100 MHz的時鐘頻率下。數據從外部進入SOPC系統的過程中由于時鐘的不匹配,極易造成數據重復或丟失,而異步FIFO正是解決這個問題的關鍵。采用異步FI FO作為數據緩沖接口,低速時鐘域接收來自視頻解碼模塊的Raw Data圖像數據,完成寫FIFO操作;高速時鐘域響應DMA控制器的讀請求,由DMA控制器完成讀FIFO操作。

多路視頻數據存儲接口模塊通過SOPC的自定義外設實現,本設計針對多路視頻數據采集,可根據每路視頻數據的不同格式單獨為每路視頻數據定制存儲接口。這種設計一方面降低了系統硬件結構的復雜度,另一方面保證每路數據獨立并行傳輸,提高數據采集的效率。自定義外設接口遵循Avalon總線協議,根據發起數據操作的方式不同,分為Master和Slave兩種,本系統的多路數據存儲接口模塊采用Salve模式。

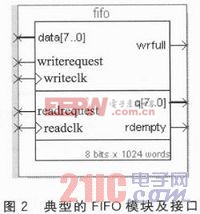

自定義存儲接口模塊以FIFO IP Core為核心,通過與Avalon總線協議匹配,接收NiosII處理器的控制信號。該模塊利用QuartusII中Mega Wizard Plug-In Manager實例化FIFO IP Core,根據數據格式和系統資源綜合考慮,FIFO的數據寬度為8位,FIFO深度為1024。在這里保留FI FO IP Core的讀時鐘信號readclk、讀請求信號readrequest、8位讀取數據接口q[7:0]、8位寫入數據接口 data[7:0]、寫時鐘信號writec lk、寫請求信號writerequest以及FIFO空狀態信號rdempty。實例化后的FIFO模塊如圖2所示。

評論